# **ICs for Communications**

DSP Oriented PBX Controller DOC

PEB 20560 Version 2.1

Preliminary Data Sheet 11.97

| PEB 20560                        |                                 |                                                |

|----------------------------------|---------------------------------|------------------------------------------------|

| Revision His                     | story:                          | Current Version: Preliminary Data Sheet 11.97  |

| Previous Vei                     | sion:                           | Preliminary Data Sheet 03.97                   |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision)   |

|                                  |                                 | Global Interrupt Status Register (Version 2.1) |

|                                  |                                 | Interrupt Mask Register for GPIO (Version 2.1) |

#### Edition 11.97

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1997.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table of Contents |                                                            | Page |

|-------------------|------------------------------------------------------------|------|

| 1                 | Overview                                                   | 1-1  |

| 1.1               | DOC Features                                               |      |

| 1.2               | Logic Symbol                                               |      |

| 1.3               | Pin Configuration                                          |      |

| 1.4               | Pin Description                                            |      |

| 1.5               | Functional Block Diagram and System Integration            |      |

| 1.6               | Example for System Integration                             |      |

| 2                 | Functional Block Description                               | 2-1  |

| 2.1               | ELIC0 and ELIC1                                            |      |

| 2.1.1             | General Functions and Device Architecture                  |      |

| 2.1.2             | Functional Blocks                                          |      |

| 2.1.2.1           | Watchdog Timer                                             |      |

| 2.1.2.2           | Reset Logic                                                |      |

| 2.1.2.3           | EPIC®-1                                                    |      |

| 2.1.2.3.1         | PCM-Interface                                              |      |

| 2.1.2.3.2         | Configurable Interface                                     |      |

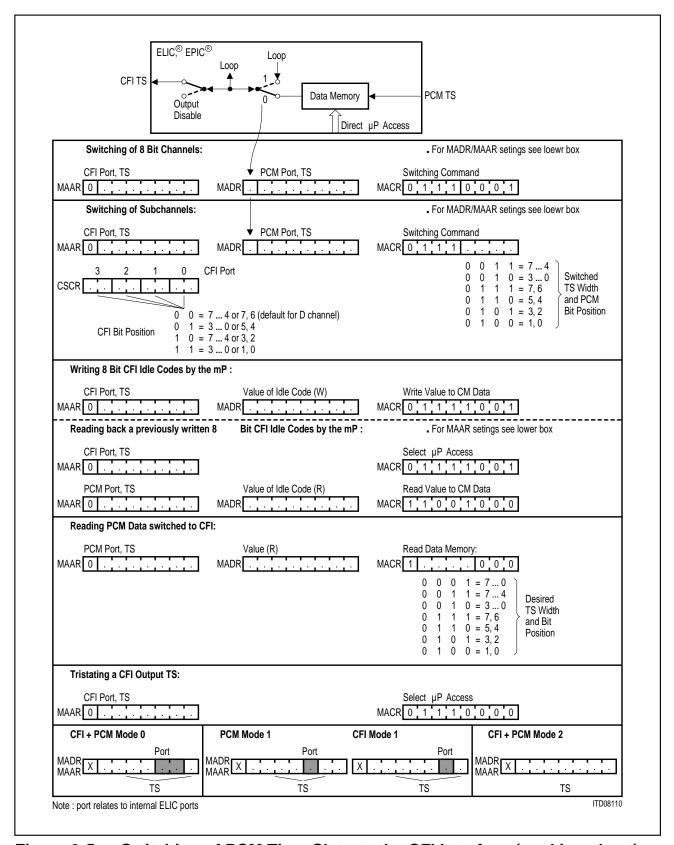

| 2.1.2.3.3         | Memory Structure and Switching                             |      |

| 2.1.2.3.4         | Pre-processed Channels, Layer-1 Support                    |      |

| 2.1.2.3.5         | Special Functions                                          |      |

| 2.1.2.4           | SACCO                                                      |      |

| 2.1.2.4.1         | Block Diagram                                              |      |

| 2.1.2.4.2         | Parallel Interface                                         |      |

| 2.1.2.4.3         | FIFO-Structure                                             |      |

| 2.1.2.4.4         | Protocol Support                                           |      |

| 2.1.2.4.5         | Special Functions                                          |      |

| 2.1.2.4.6         | Serial Interface                                           |      |

| 2.1.2.4.7         | Serial Port Configuration                                  |      |

| 2.1.2.4.8         | Test Mode                                                  |      |

| 2.1.2.5           | D-Channel Arbiter                                          |      |

| 2.1.2.5.1         | Upstream Direction                                         |      |

| 2.1.2.5.2         | Downstream Direction                                       |      |

| 2.1.2.5.3         | Control Channel Delay                                      | 2-39 |

| 2.1.2.5.4         | D-Channel Arbiter Co-operating with QUAT-S Circuits        | 2-40 |

| 2.2               | SIDEC                                                      |      |

| 2.3               | Multiplexers                                               | 2-42 |

| 2.3.1             | IOM®- and PCM-Ports Multiplexers                           |      |

| 2.3.1.1           | IOM® Multiplexer for IOM®-2 Ports (CFI Interfaces of EPIC) |      |

| 2.3.1.2           | PCM-Ports Multiplexer for PCM Highways                     |      |

| 2.3.2             | Multiplexers for Signaling Controllers                     |      |

| 2.3.2.1           | SACCO-A0 and SACCO-A1                                      |      |

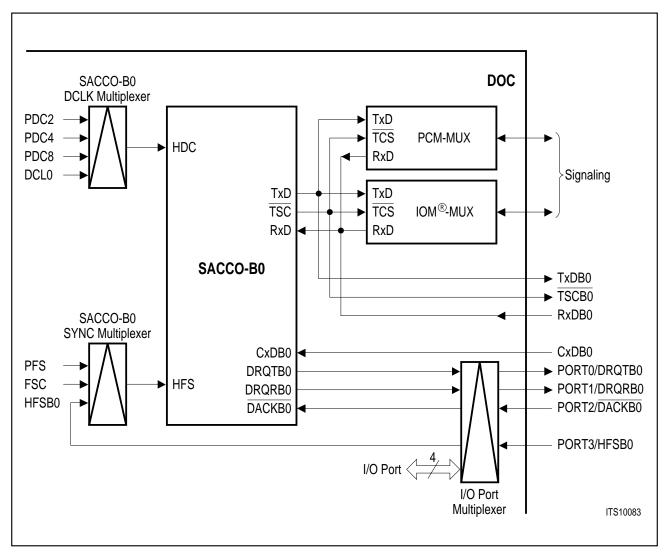

| 2.3.2.2           | SACCO-B0                                                   |      |

| Table of C | Contents                                                   | Page   |

|------------|------------------------------------------------------------|--------|

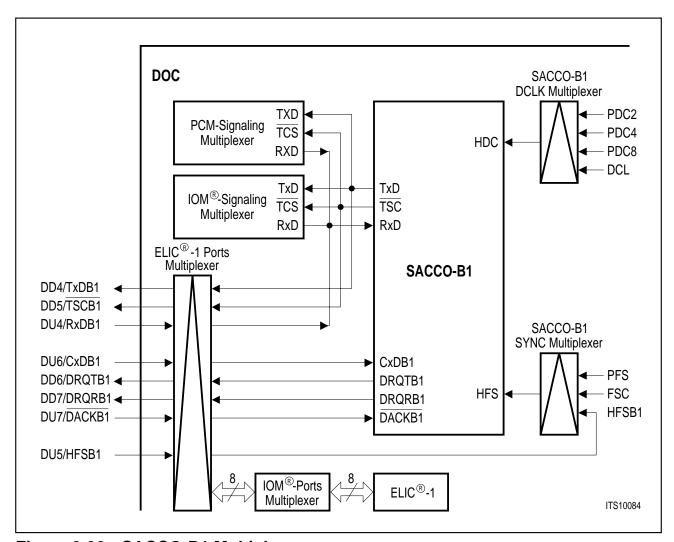

| 2.3.2.3    | SACCO-B1                                                   | . 2-49 |

| 2.3.2.4    | SIDEC                                                      | . 2-50 |

| 2.3.3      | ELIC1-Ports Multiplexer                                    | . 2-51 |

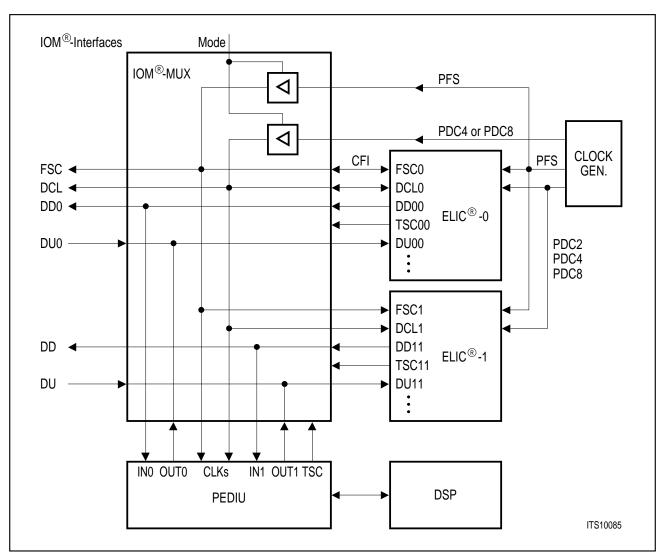

| 2.3.4      | IOM®-Multiplexer for DSP Connection to EPICs               | . 2-52 |

| 2.3.5      | PCM/IOM MUX Registers Description                          | . 2-53 |

| 2.3.5.1    | PCM/IOM MUX Mode Register (MMODE)                          | . 2-53 |

| 2.3.5.2    | CFI Channel Select 0 Register (MCCHSEL0)                   | . 2-54 |

| 2.3.5.3    | CFI Channel Select 1 Register (MCCHSEL1)                   | . 2-55 |

| 2.3.5.4    | CFI Channel Select 2 Register (MCCHSEL2)                   | . 2-56 |

| 2.3.5.5    | PCM Channel Select 0 Register (MPCHSEL0)                   | . 2-57 |

| 2.4        | Channel Indication Logic (CHI)                             | . 2-58 |

| 2.4.1      | CHI Configuration Register (VMODR)                         | . 2-58 |

| 2.4.2      | CHI Control Registers (VDATR0:VDATR3)                      |        |

| 2.5        | FSC with Delay (FSCD)                                      |        |

| 2.6        | Digital Signal Processor (DSP)                             |        |

| 2.6.1      | DSP Kernel Block Diagram                                   |        |

| 2.6.2      | DSP Instruction Set                                        | . 2-61 |

| 2.7        | DSP Control Unit (DCU)                                     |        |

| 2.7.1      | General                                                    |        |

| 2.7.2      | DSP Address Decoding                                       |        |

| 2.7.3      | Control of External Memories / Registers                   | . 2-63 |

| 2.7.3.1    | Memory Configuration Register (MEMCONFR)                   |        |

| 2.7.3.2    | Test Configuration Register (TESTCONFR)                    |        |

| 2.7.4      | Emulation Support                                          | . 2-70 |

| 2.7.5      | Interrupt Handling and Test Support                        |        |

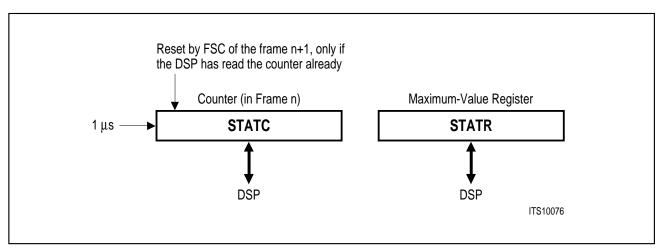

| 2.7.6      | Run Time Statistics Counter and Register (STATC and STATR) | . 2-71 |

| 2.7.7      | Program Write Protection Register (PASSR)                  | . 2-73 |

| 2.7.8      | Serial (via JTAG) Emulation Configuration Register (JCONF) | . 2-73 |

| 2.7.9      | Boot Support                                               |        |

| 2.7.9.1    | Boot Sequence                                              | . 2-74 |

| 2.7.9.2    | Emulation Boot                                             | . 2-75 |

| 2.7.9.3    | Boot Procedure                                             | . 2-75 |

| 2.7.9.4    | Boot ROM                                                   | . 2-75 |

| 2.7.9.5    | μP Boot                                                    | . 2-76 |

| 2.7.9.6    | Mail Box Instructions Format                               |        |

| 2.7.9.7    | Write Program Memory Command                               | . 2-77 |

| 2.7.9.8    | OAK Opcodes                                                |        |

| 2.7.9.9    | Boot Configuration Register (BOOTCONF)                     |        |

| 2.7.9.10   | The Bootroutine                                            |        |

| 2.7.10     | Sine Table ROM                                             |        |

| 2.8        | PCM-DSP Interface Unit (PEDIU)                             |        |

| 2.8.1      | General Description                                        | . 2-88 |

| Table of C | Contents                                             | Page  |

|------------|------------------------------------------------------|-------|

| 2.8.2      | PEDIU Internal Registers                             | 2-93  |

| 2.8.2.1    | PEDIU Control Register (UCR)                         |       |

| 2.8.2.2    | PEDIU Status Register (USR)                          |       |

| 2.8.2.3    | PEDIU Input Stream Bypass Enable Register (UISBPER)  | 2-101 |

| 2.8.2.4    | PEDIU Output Stream Bypass Enable Register (UOSBPER) | 2-103 |

| 2.8.2.5    | PEDIU Tri-State Register (UTSR)                      |       |

| 2.8.2.6    | PEDIU ROM Test Address Register (UPRTAR) and         |       |

|            | PEDIU ROM Test Data Register (UPRTDR)                | 2-106 |

| 2.8.3      | PEDIU Synchronization and Clock Rates                |       |

| 2.8.3.1    | PEDIU Synchronization by FSC and DCL                 |       |

| 2.8.3.2    | Restrictions on PEDIU Clock Rates                    | 2-108 |

| 2.8.4      | PEDIU Address Space                                  |       |

| 2.8.5      | PEDIU Data Processing                                |       |

| 2.8.5.1    | PEDIU Serial Data Processing                         |       |

| 2.8.5.2    | PEDIU Parallel Data Processing                       |       |

| 2.8.5.3    | The Circular Buffer Address Method                   |       |

| 2.8.6      | a-/μ-law Conversion                                  |       |

| 2.9        | On-chip Emulation (OCEM)                             |       |

| 2.10       | Mailbox                                              |       |

| 2.10.1     | μP Mailbox                                           | 2-115 |

| 2.10.2     | OAK Mailbox                                          |       |

| 2.11       | μP Interface                                         | 2-118 |

| 2.11.1     | Compatibility                                        |       |

| 2.11.2     | Memory and I/O Organization                          |       |

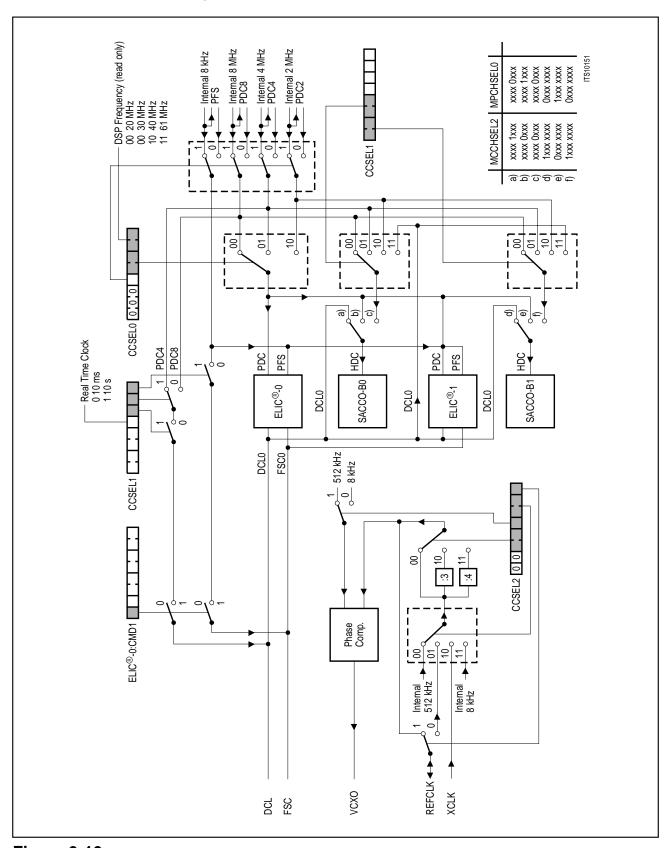

| 2.12       | Clock Generator                                      |       |

| 2.12.1     | Block Diagram                                        |       |

| 2.12.2     | Types of Clock Signals                               | 2-120 |

| 2.12.2.1   | Input/Output Clocks                                  |       |

| 2.12.2.2   | Clock Selection                                      | 2-120 |

| 2.12.3     | Clocks Generator Registers Description               | 2-125 |

| 2.12.3.1   | Clocks Select 0 Register (CCSEL0)                    | 2-125 |

| 2.12.3.2   | Clocks Select 1 Register (CCSEL1)                    |       |

| 2.12.3.3   | Clocks Select 2 Register (CCSEL2)                    |       |

| 2.13       | Interrupt Controller                                 |       |

| 2.13.1     | MASK (IMASK0, IMASK1)                                | 2-129 |

| 2.13.2     | Interrupt Sources                                    |       |

| 2.13.3     | Interrupt Priority (IPAR0, IPAR1, IPAR2)             |       |

| 2.13.4     | Interrupt Cascading                                  |       |

| 2.13.4.1   | Slave Mode                                           |       |

| 2.13.4.2   | Daisy Chaining                                       |       |

| 2.13.5     | Global Interrupt Status Registers (IGIS0 and IGIS1)  |       |

| 2 14       | Universal Asynchronous Receiver/Transmitter (UART)   |       |

| Table of | f Contents                                  | Page  |

|----------|---------------------------------------------|-------|

| 2.14.1   | Registers Overview                          | 2-139 |

| 2.14.1.1 | Line Control Register (LCR)                 |       |

| 2.14.1.2 | Programmable Baud Rate Generator (Divisors) | 2-144 |

| 2.14.1.3 | Line Status Register (LSR)                  | 2-145 |

| 2.14.1.4 |                                             |       |

| 2.14.1.5 | Interrupt Identification Register (IIR)     | 2-149 |

| 2.14.1.6 | Interrupt Enable Register (IER)             | 2-151 |

| 2.14.1.7 | Modem Control Register (MCR)                | 2-151 |

| 2.14.1.8 | Modem Status Register (MSR)                 | 2-153 |

| 2.14.1.9 | Scratchpad Register (SCR)                   | 2-154 |

| 2.14.2   | FIFO Interrupt Mode Operation               | 2-154 |

| 2.14.3   | FIFO Polled Mode Operation                  | 2-155 |

| 2.15     | General Purpose I/O Port (GPIO)             | 2-156 |

| 2.15.1   | I/O Port Support Lines (Mode 0)             | 2-156 |

| 2.15.2   | SACCO-B0 Support Lines (Mode 1)             | 2-156 |

| 2.15.3   | UART Support Lines (Mode 2)                 |       |

| 2.15.4   | Configuration Register (VCFGR)              | 2-157 |

| 2.15.5   | Data Register (VDATR)                       |       |

| 2.15.6   | Version Number Register (VNR)               | 2-158 |

| 2.16     | Boundary Scan Support (JTAG)                | 2-158 |

| 2.16.1   | Boundary Scan                               |       |

| 2.16.2   | TAP-Controller                              | 2-159 |

| 2.17     | Reset Logic                                 | 2-160 |

| 3        | Operational Description                     | 3-1   |

| 3.1      | ELIC0 and ELIC1                             |       |

| 3.1.1    | Interrupt Structure and Logic               |       |

| 3.1.2    | Clocking                                    |       |

| 3.1.3    | EPIC®-1 Operation                           |       |

| 3.1.3.1  | PCM-Interface                               |       |

| 3.1.3.2  | Configurable Interface                      |       |

| 3.1.3.3  | Switching Functions                         |       |

| 3.1.3.4  | Special Functions                           |       |

| 3.1.4    | SACCO-A/B                                   |       |

| 3.1.4.1  | Data Transmission in Interrupt Mode         |       |

| 3.1.4.2  | Data Transmission in DMA-Mode               |       |

| 3.1.4.3  | Data Reception in Interrupt Mode            |       |

| 3.1.4.4  | Data Reception in DMA-Mode                  |       |

| 3.1.5    | D-Channel Arbiter                           |       |

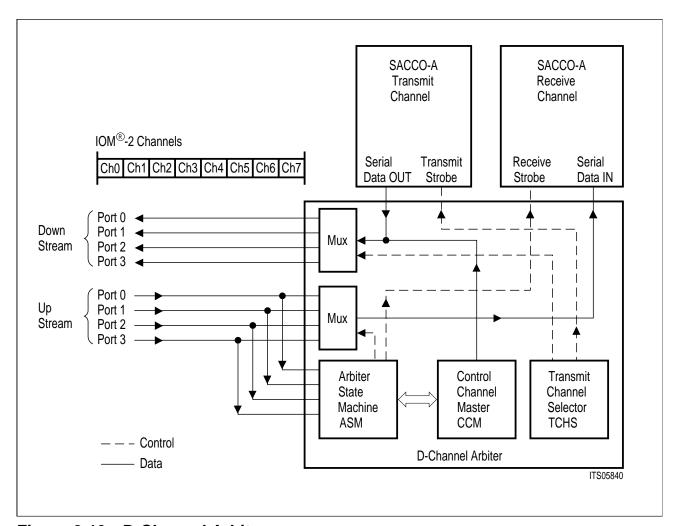

| 3.1.5.1  | SACCO-A Transmission                        | 3-15  |

| 3.1.5.2  | SACCO-A Reception                           | 3-16  |

| 3.1.6    | Initialization Procedure                    | 3-17  |

| Table of 0 | Contents                                                        | Page   |

|------------|-----------------------------------------------------------------|--------|

| 3.1.6.1    | Hardware Reset                                                  | . 3-17 |

| 3.1.6.2    | EPIC®-1 Initialization                                          | . 3-17 |

| 3.1.6.2.1  | EPIC® Registers Initialization                                  | . 3-17 |

| 3.1.6.2.2  | Control Memory Reset                                            | . 3-17 |

| 3.1.6.2.3  | Initialization of Pre-processed Channels                        | . 3-18 |

| 3.1.6.2.4  | Initialization of the Upstream Data Memory (DM) Tri-State Field |        |

| 3.1.6.3    | SACCO-Initialization                                            |        |

| 3.1.6.4    | Initialization of D-Channel Arbiter                             |        |

| 3.1.6.5    | Activation of the PCM- and CFI-Interfaces                       |        |

| 3.1.6.6    | Initialization Example                                          | . 3-23 |

| 3.1.6.6.1  | EPIC®-1 Initialization Example                                  |        |

| 3.1.6.6.2  | SACCO-A Initialization Example                                  |        |

| 3.1.6.6.3  | D-Channel Arbiter Initialization Example                        |        |

| 3.1.6.6.4  | PCM- and CFI-Interface Activation Example                       | . 3-27 |

| 3.1.6.6.5  | SACCO-B Initialization Example                                  |        |

| 3.2        | SIDEC                                                           | . 3-28 |

| 4          | DSP Core OAK                                                    | 4-1    |

| 4.1        | Introduction                                                    | 4-1    |

| 4.1.1      | General Description                                             | 4-1    |

| 4.1.2      | Architecture Highlights                                         | 4-1    |

| 4.2        | Architecture Features                                           | 4-3    |

| 4.2.1      | Features                                                        | 4-3    |

| 4.2.2      | Buses                                                           | 4-4    |

| 4.2.2.1    | Data Buses                                                      | 4-4    |

| 4.2.2.2    | Program Buses                                                   | 4-4    |

| 4.2.3      | Memory Spaces and Organization                                  | 4-5    |

| 4.2.3.1    | Program Memory                                                  | 4-5    |

| 4.2.3.2    | Data Memory                                                     | 4-6    |

| 4.3        | Development Tools                                               | 4-7    |

| 4.3.1      | COFF Macro Assembler                                            | 4-7    |

| 4.3.2      | Linker/Locator                                                  | 4-7    |

| 4.3.3      | Object Format Convertor                                         | 4-7    |

| 4.3.4      | ANSI C-Compiler                                                 | 4-7    |

| 4.3.5      | Simulator                                                       | 4-8    |

| 4.3.6      | Debugger                                                        | 4-8    |

| 5          | Description of Registers                                        | 5-1    |

| 5.1        | μP Address Space Register Overview                              |        |

| 5.1.1      | ELIC0 and ELIC1 Registers Description                           |        |

| 5.1.1.1    | Interrupt Top Level                                             |        |

| 5.1.1.1.1  | Interrupt Status Register (ISTA)                                |        |

| Table of Contents P |                                                             | Page |

|---------------------|-------------------------------------------------------------|------|

| 5.1.1.1.2           | Mask Register (MASK)                                        | 5-23 |

| 5.1.1.2             | Watchdog Timer (in ELIC0 only)                              | 5-23 |

| 5.1.1.2.1           | Watchdog Control Register (WTC)                             |      |

| 5.1.1.3             | ELIC® Mode Register                                         |      |

| 5.1.1.4             | EPIC®-1                                                     |      |

| 5.1.1.4.1           | PCM-Mode Register (PMOD)                                    |      |

| 5.1.1.4.2           | Bit Number per PCM-Frame (PBNR)                             | 5-28 |

| 5.1.1.4.3           | PCM-Offset Downstream Register (POFD)                       | 5-28 |

| 5.1.1.4.4           | PCM-Offset Upstream Register (POFU)                         | 5-29 |

| 5.1.1.4.5           | PCM-Clock Shift Register; within the ELIC (PCSR)            | 5-29 |

| 5.1.1.4.6           | PCM-Input Comparison Mismatch (PICM)                        | 5-30 |

| 5.1.1.4.7           | Configurable Interface Mode Register 1 (CMD1)               | 5-30 |

| 5.1.1.4.8           | Configurable Interface Mode Register 2 (CMD2)               | 5-33 |

| 5.1.1.4.9           | Configurable Interface Bit Number Register (CBNR)           | 5-34 |

| 5.1.1.4.10          | Configurable Interface Time-Slot Adjustment Register (CTAR) | 5-35 |

| 5.1.1.4.11          | Configurable Interface Bit Shift Register (CBSR)            | 5-35 |

| 5.1.1.4.12          | Configurable Interface Subchannel Register (CSCR)           | 5-37 |

| 5.1.1.4.13          | Memory Access Control Register (MACR)                       | 5-38 |

| 5.1.1.4.14          | Memory Access Address Register (MAAR)                       | 5-42 |

| 5.1.1.4.15          | Memory Access Data Register (MADR)                          | 5-43 |

| 5.1.1.4.16          | Synchronous Transfer Data Register (STDA)                   | 5-43 |

| 5.1.1.4.17          | Synchronous Transfer Data Register B (STDB)                 | 5-43 |

| 5.1.1.4.18          | Synchronous Transfer Receive Address Register A (SARA)      |      |

| 5.1.1.4.19          | Synchronous Transfer Receive Address Register B (SARB)      | 5-44 |

| 5.1.1.4.20          | Synchronous Transfer Transmit Address Register A (SAXA) .   | 5-45 |

| 5.1.1.4.21          | Synchronous Transfer Transmit Address Register B (SAXB) .   | 5-45 |

| 5.1.1.4.22          | Synchronous Transfer Control Register (STCR)                | 5-46 |

| 5.1.1.4.23          | MF-Channel Active Indication Register (MFAIR)               | 5-47 |

| 5.1.1.4.24          | MF-Channel Subscriber Address Register (MFSAR)              | 5-47 |

| 5.1.1.4.25          | Monitor/Feature Control Channel FIFO (MFFIFO)               | 5-48 |

| 5.1.1.4.26          | Signaling FIFO (CIFIFO)                                     | 5-48 |

| 5.1.1.4.27          | Timer Register (TIMR)                                       | 5-49 |

| 5.1.1.4.28          | Status Register EPIC®-1 (STAR_E)                            | 5-49 |

| 5.1.1.4.29          | Command Register EPIC®-1 (CMDR_E)                           | 5-50 |

| 5.1.1.4.30          | Interrupt Status Register EPIC®-1 (ISTA_E)                  | 5-52 |

| 5.1.1.4.31          | Mask Register EPIC®-1 (MASK_E)                              | 5-53 |

| 5.1.1.4.32          | Operation Mode Register (OMDR)                              | 5-54 |

| 5.1.1.4.33          | Version Number Status Register (VNSR)                       | 5-56 |

| 5.1.1.5             | SACCO-A Register Description                                | 5-56 |

| 5.1.1.5.1           | Receive FIFO (RFIFO)                                        |      |

| 5.1.1.5.2           | Transmit FIFO (XFIFO)                                       | 5-57 |

| 5.1.1.5.3           | Interrupt Status Register (ISTA_A/B)                        | 5-57 |

| Table of Contents |                                             | Page |

|-------------------|---------------------------------------------|------|

| 5.1.1.5.4         | Mask Register (MASK_A/B)                    | 5-57 |

| 5.1.1.5.5         | Extended Interrupt Register (EXIR_A/B)      | 5-58 |

| 5.1.1.5.6         | Command Register (CMDR)                     |      |

| 5.1.1.5.7         | Mode Register (MODE)                        |      |

| 5.1.1.5.8         | Channel Configuration Register 1 (CCR1)     |      |

| 5.1.1.5.9         | Channel Configuration Register 2 (CCR2)     |      |

| 5.1.1.5.10        | Receive Length Check Register (RLCR)        |      |

| 5.1.1.5.11        | Status Register (STAR)                      |      |

| 5.1.1.5.12        | Receive Status Register (RSTA)              | 5-63 |

| 5.1.1.5.13        | Receive HDLC-Control Register (RHCR)        |      |

| 5.1.1.5.14        | Transmit Address Byte 1 (XAD1)              |      |

| 5.1.1.5.15        | Transmit Address Byte 2 (XAD2)              |      |

| 5.1.1.5.16        | Receive Address Byte Low Register 1 (RAL1)  |      |

| 5.1.1.5.17        | Receive Address Byte Low Register 2 (RAL2)  |      |

| 5.1.1.5.18        | Receive Address Byte High Register 1 (RAH1) |      |

| 5.1.1.5.19        | Receive Address Byte High Register 2 (RAH2) |      |

| 5.1.1.5.20        | Receive Byte Count Low (RBCL)               |      |

| 5.1.1.5.21        | Receive Byte Count High (RBCH)              |      |

| 5.1.1.5.22        | Version Status Register (VSTR)              |      |

| 5.1.1.6           | SACCO-B Register Description                |      |

| 5.1.1.6.1         | Receive FIFO (RFIFO)                        |      |

| 5.1.1.6.2         | Transmit FIFO (XFIFO)                       |      |

| 5.1.1.6.3         | Interrupt Status Register (ISTA_A/B)        |      |

| 5.1.1.6.4         | Mask Register (MASK_A/B)                    |      |

| 5.1.1.6.5         | Extended Interrupt Register (EXIR_A/B)      |      |

| 5.1.1.6.6         | Command Register (CMDR)                     |      |

| 5.1.1.6.7         | Mode Register (MODE)                        |      |

| 5.1.1.6.8         | Channel Configuration Register 1 (CCR1)     | 5-75 |

| 5.1.1.6.9         | Channel Configuration Register 2 (CCR2)     |      |

| 5.1.1.6.10        | Receive Length Check Register (RLCR)        | 5-78 |

| 5.1.1.6.11        | Status Register (STAR)                      |      |

| 5.1.1.6.12        | Receive Status Register (RSTA)              |      |

| 5.1.1.6.13        | Receive HDLC-Control Register (RHCR)        |      |

| 5.1.1.6.14        | Transmit Address Byte 1 (XAD1)              |      |

| 5.1.1.6.15        | Transmit Address Byte 2 (XAD2)              |      |

| 5.1.1.6.16        | Receive Address Byte Low Register 1 (RAL1)  |      |

| 5.1.1.6.17        | Receive Address Byte Low Register 2 (RAL2)  | 5-83 |

| 5.1.1.6.18        | Receive Address Byte High Register 1 (RAH1) |      |

| 5.1.1.6.19        | Receive Address Byte High Register 2 (RAH2) |      |

| 5.1.1.6.20        | Receive Byte Count Low (RBCL)               |      |

| 5.1.1.6.21        | Receive Byte Count High (RBCH)              |      |

| 5.1.1.6.22        | Transmit Byte Count Low (XBCL)              |      |

| Table of Contents P |                                               | Page  |

|---------------------|-----------------------------------------------|-------|

| 5.1.1.6.23          | Transmit Byte Count High (XBCH)               | 5-85  |

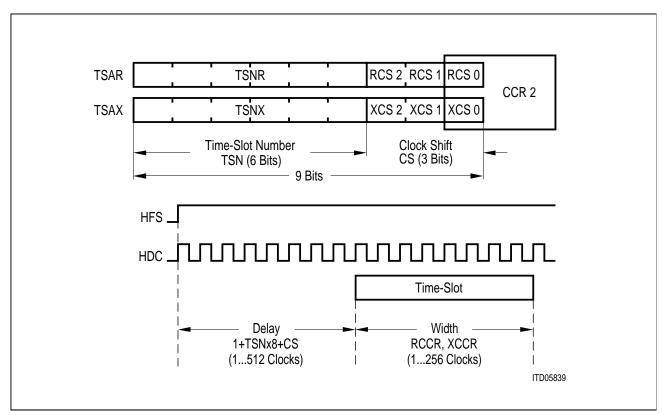

| 5.1.1.6.24          | Time-Slot Assignment Register Transmit (TSAX) | 5-85  |

| 5.1.1.6.25          | Time-Slot Assignment Register Receive (TSAR)  |       |

| 5.1.1.6.26          | Transmit Channel Capacity Register (XCCR)     |       |

| 5.1.1.6.27          | Receive Channel Capacity Register (RCCR)      |       |

| 5.1.1.6.28          | Version Status Register (VSTR)                |       |

| 5.1.1.7             | D-Channel Arbiter Registers                   | 5-87  |

| 5.1.1.7.1           | Arbiter Mode Register (AMO)                   | 5-87  |

| 5.1.1.7.2           | Arbiter State Register (ASTATE)               | 5-88  |

| 5.1.1.7.3           | Suspend Counter Value Register (SCV)          | 5-88  |

| 5.1.1.7.4           | D-Channel Enable Register IOM®-Port 0 (DCE0)  | 5-89  |

| 5.1.1.7.5           | D-Channel Enable Register IOM®-Port 1 (DCE1)  |       |

| 5.1.1.7.6           | D-Channel Enable Register IOM®-Port 2 (DCE2)  |       |

| 5.1.1.7.7           | D-Channel Enable Register IOM®-Port 3 (DCE3)  | 5-89  |

| 5.1.1.7.8           | Transmit D-Channel Address Register (XDC)     |       |

| 5.1.1.7.9           | Broadcast Group IOM®-Port 0 (BCG0)            | 5-90  |

| 5.1.1.7.10          | Broadcast Group IOM®-Port 1 (BCG1)            | 5-90  |

| 5.1.1.7.11          | Broadcast Group IOM®-Port 2 (BCG2)            | 5-90  |

| 5.1.1.7.12          | Broadcast Group IOM®-Port 3 (BCG3)            | 5-91  |

| 5.1.2               | SIDEC Register Description                    | 5-91  |

| 5.1.2.1             | Receive FIFO (RFIFO)                          | 5-91  |

| 5.1.2.2             | Transmit FIFO (XFIFO)                         | 5-91  |

| 5.1.2.3             | Interrupt Status Register (ISTA_A/B)          | 5-92  |

| 5.1.2.4             | Mask Register (MASK_A/B)                      | 5-92  |

| 5.1.2.5             | Extended Interrupt Register (EXIR_A/B)        | 5-93  |

| 5.1.2.6             | Command Register (CMDR)                       | 5-94  |

| 5.1.2.7             | Mode Register (MODE)                          |       |

| 5.1.2.8             | Channel Configuration Register 1 (CCR1)       | 5-97  |

| 5.1.2.9             | Channel Configuration Register 2 (CCR2)       |       |

| 5.1.2.10            | Receive Length Check Register (RLCR)          |       |

| 5.1.2.11            | Status Register (STAR)                        | 5-99  |

| 5.1.2.12            | Receive Status Register (RSTA)                |       |

| 5.1.2.13            | Receive HDLC-Control Register (RHCR)          |       |

| 5.1.2.14            | Transmit Address Byte 1 (XAD1)                |       |

| 5.1.2.15            | Transmit Address Byte 2 (XAD2)                |       |

| 5.1.2.16            | Receive Address Byte Low Register 1 (RAL1)    | 5-103 |

| 5.1.2.17            | Receive Address Byte Low Register 2 (RAL2)    |       |

| 5.1.2.18            | Receive Address Byte High Register 1 (RAH1)   |       |

| 5.1.2.19            | Receive Address Byte High Register 2 (RAH2)   |       |

| 5.1.2.20            | Receive Byte Count Low (RBCL)                 |       |

| 5.1.2.21            | Receive Byte Count High (RBCH)                |       |

| 5.1.2.22            | Time-Slot Assignment Register Transmit (TSAX) | 5-105 |

| Table of ( | Contents                                                        | Page   |

|------------|-----------------------------------------------------------------|--------|

| 5.1.2.23   | Time-Slot Assignment Register Receive (TSAR)                    | 5-106  |

| 5.1.2.24   | Transmit Channel Capacity Register (XCCR)                       |        |

| 5.1.2.25   | Receive Channel Capacity Register (RCCR)                        | 5-106  |

| 5.1.2.26   | Version Status Register (VSTR)                                  | 5-107  |

| 6          | Applications                                                    | 6-1    |

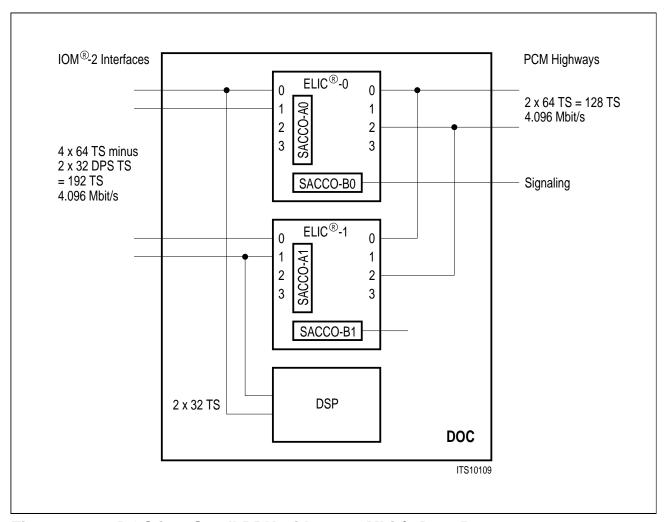

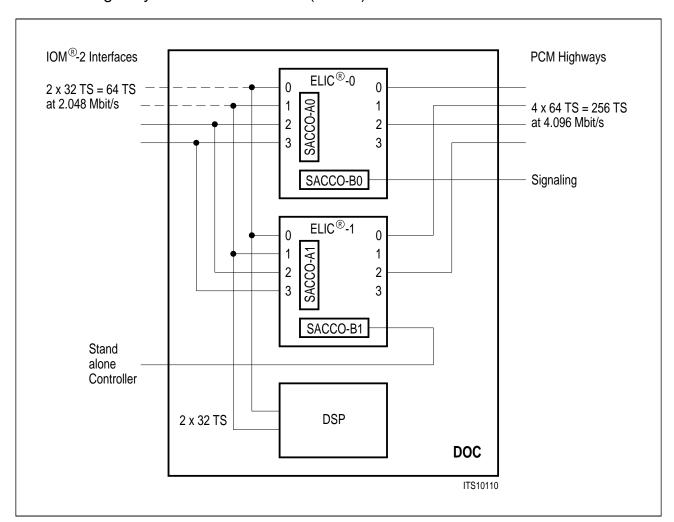

| 6.1        | DOC in a Small PBX                                              | 6-1    |

| 6.1.1      | Small PBX with 2.048 Mbit/s Data Rate                           | 6-1    |

| 6.1.2      | Small PBX with 4.096 Mbit/s Data Rate                           | 6-3    |

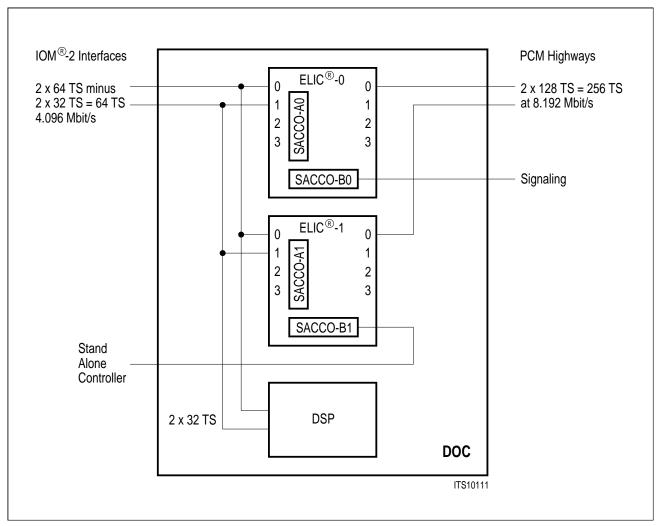

| 6.2        | DOC on Line Card                                                |        |

| 6.2.1      | Line Card with 2.048 and 4.096 Mbit/s Data Rates                |        |

| 6.2.2      | Line Card with 4.096 and 8.192 Mbit/s Data Rates                | 6-5    |

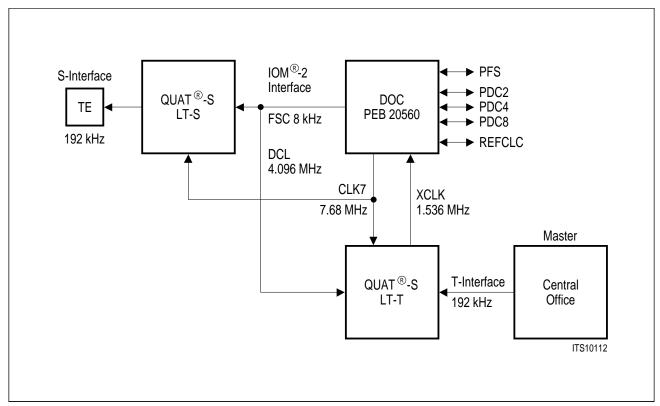

| 6.3        | Clock Generation                                                |        |

| 6.3.1      | PBX with one DOC                                                |        |

| 6.3.2      | PBX with Multiple DOCs                                          |        |

| 6.4        | Signaling with SIDEC                                            | 6-8    |

| 6.5        | Local Network Controller (SACCO-B1 as LNC)                      |        |

| 6.6        | UART Applications                                               |        |

| 6.7        | IOM®-2 Channel Indication Signal (CHI)                          |        |

| 6.8        | Use of FSCD                                                     |        |

| 6.9        | Watch-Dog Activation                                            |        |

| 6.10       | Tone and Voice Processing                                       |        |

| 6.11       | DSP Frequency Recommendation                                    | . 6-11 |

| 7          | Electrical Characteristics                                      | 7-1    |

| 7.1        | Absolute Maximum Ratings                                        | 7-1    |

| 7.2        | Operating Range                                                 | 7-1    |

| 7.3        | DC Characteristics                                              | 7-2    |

| 7.4        | Capacitances                                                    | 7-3    |

| 7.5        | Strap Pins Pull-up Resistors Specification                      |        |

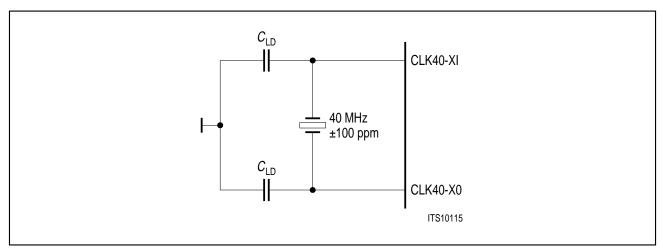

| 7.6        | 40 MHz External Crystal                                         |        |

| 7.7        | General Recommendations and Prohibitions                        | 7-4    |

| 7.8        | AC Characteristics                                              | 7-4    |

| 7.9        | Microprocessor Interface Timing                                 |        |

| 7.9.1      | PCM Interface Timing                                            |        |

| 7.9.2      | IOM®-2 Interface Timing                                         | . 7-20 |

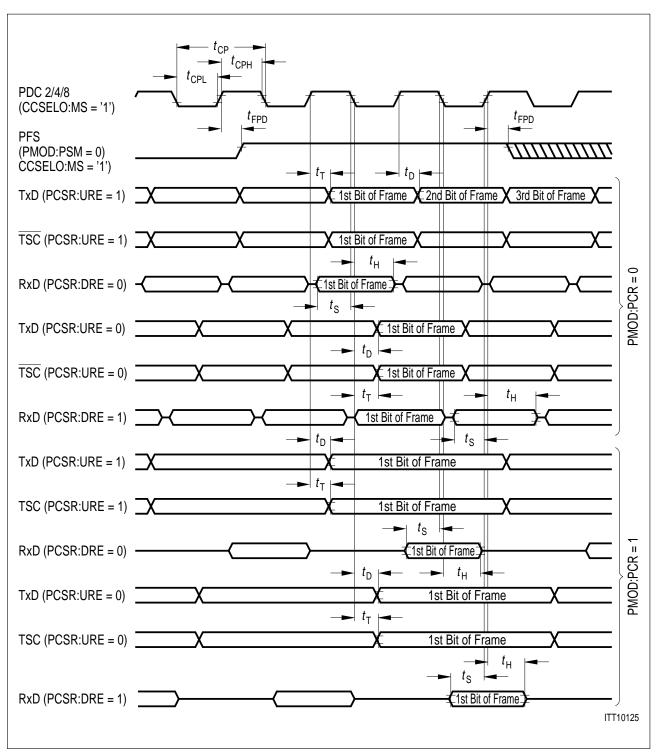

| 7.9.3      | Serial Interface Timing                                         | . 7-28 |

| 7.9.4      | Reset Timing                                                    |        |

| 7.9.5      | Boundary Scan Timing                                            |        |

| 7.9.6      | DSP External Memory Interface Timing                            |        |

| 7.9.7      | Clocks Signals Timing (additional to the IOM®-2 and PCM clocks) | . 7-45 |

| Table o | of Contents                                                     | Page |

|---------|-----------------------------------------------------------------|------|

| 8       | Ordering Information and Mechanical Data                        | 8-1  |

| 8.1     | Package Outlines                                                | 8-1  |

| 9       | Appendix                                                        | 9-1  |

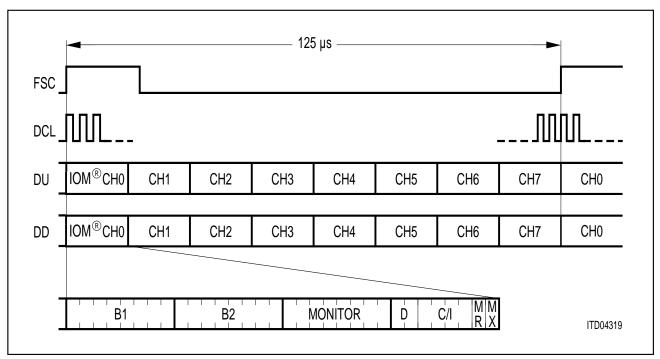

| 9.1     | IOM®-2 Interface                                                | 9-1  |

| 9.1.1   | Signals / Channels                                              | 9-1  |

| 9.1.2   | Monitor and C/I Handlers                                        | 9-2  |

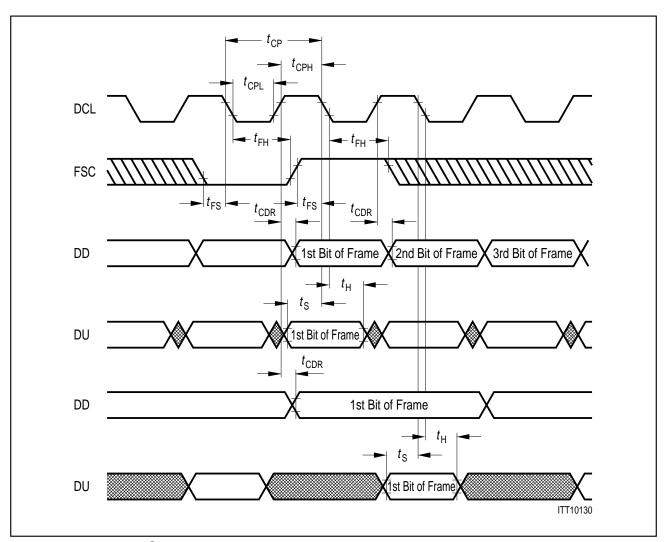

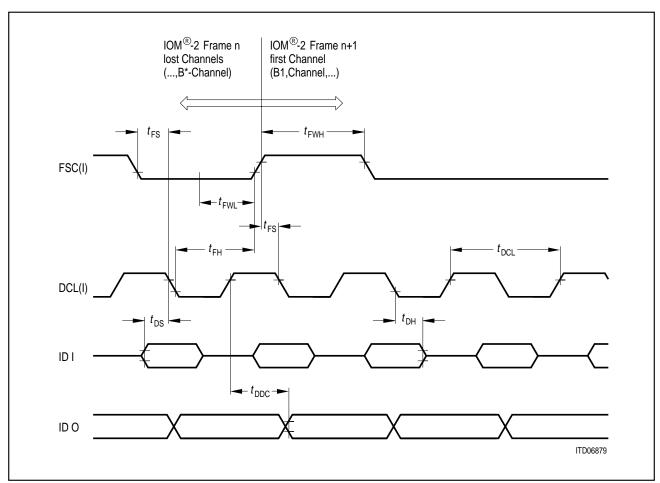

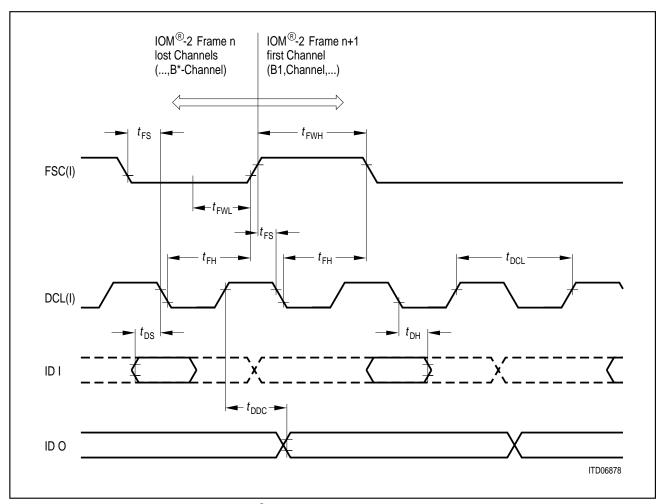

| 9.1.3   | IOM®-2 Interface Timing                                         | 9-2  |

| 9.2     | Working Sheets for Multiplexers Programming                     |      |

| 9.3     | Working Sheets                                                  |      |

| 9.3.1   | Register Summary for EPIC® Initialization                       |      |

| 9.3.2   | Switching of PCM Time-Slots to the CFI Interface                |      |

|         | (Data Downstream)                                               | 9-9  |

| 9.3.3   | Switching of CFI Time-Slots to the PCM Interface (Data Upstream |      |

| 9.3.4   | Preparing EPICs C/I Channels                                    | ,    |

| 9.3.5   | Receiving and Transmitting IOM®-2 C/I-Codes                     |      |

| 9.3.6   | DOC Port and Signaling Multiplexers                             |      |

| 9.3.7   | DOC Clocking Multiplexers                                       |      |

| 9.4     | Development Tools and Software Support                          |      |

| 9.4.1   | Software                                                        |      |

| 9.4.2   | Macro Assembler                                                 | 9-15 |

| 9.4.3   | Linker/Locator                                                  | 9-15 |

| 9.4.4   | C Compiler                                                      | 9-15 |

| 9.4.5   | Object Format Converter                                         |      |

| 9.4.6   | Simulator                                                       |      |

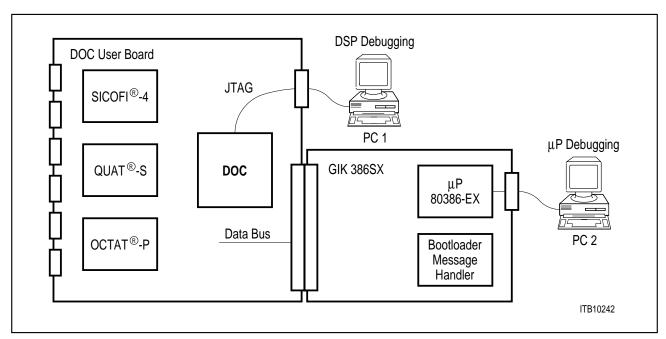

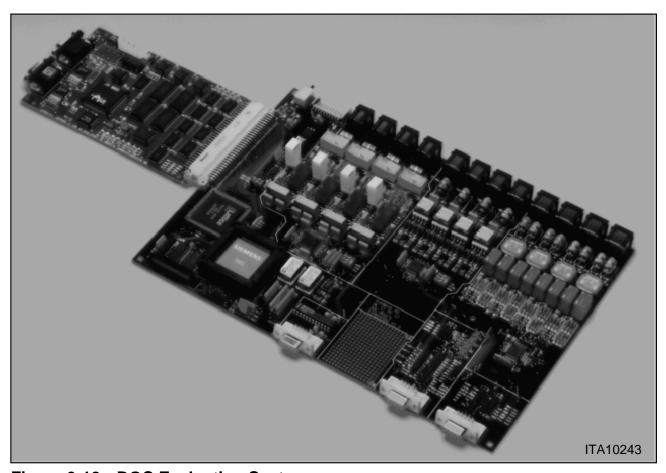

| 9.5     | OAK Development / Evaluation Board                              | 9-16 |

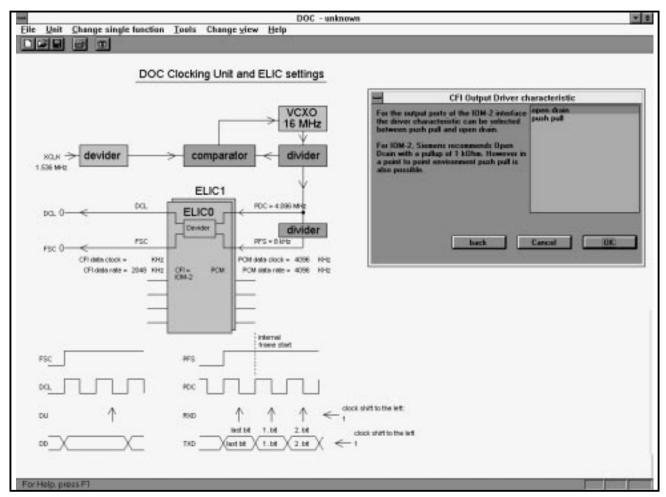

| 9.6     | DOC Configurator                                                |      |

| 10      | Acronym                                                         | 10-1 |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

| List of Figu | ires                                                                 | Page   |

|--------------|----------------------------------------------------------------------|--------|

| Figure 1-1   | Functional Blocks of a PBX                                           | 1-1    |

| Figure 1-2   | Application Example                                                  |        |

| _            | PBX for 32 Subscribers with 4 Trunk Lines using one DOC              | 1-2    |

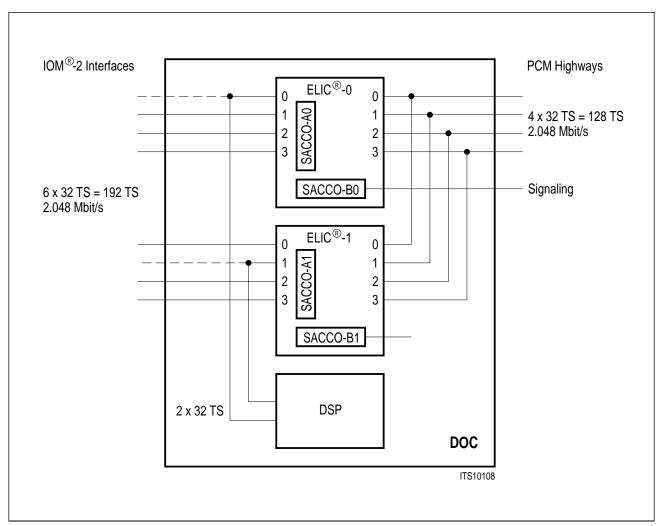

| Figure 1-3   | Principle Block Diagram of the DOC                                   | 1-4    |

| Figure 1-4   | DOC Logic Symbol                                                     | 1-7    |

| Figure 1-5   | DOC Pin Configuration (P-MQFP-160 Package)                           | 1-8    |

| Figure 1-6   | Functional Block Diagram and System Integration                      | . 1-25 |

| Figure 1-7   | Example for a PBX with one DOC                                       | . 1-26 |

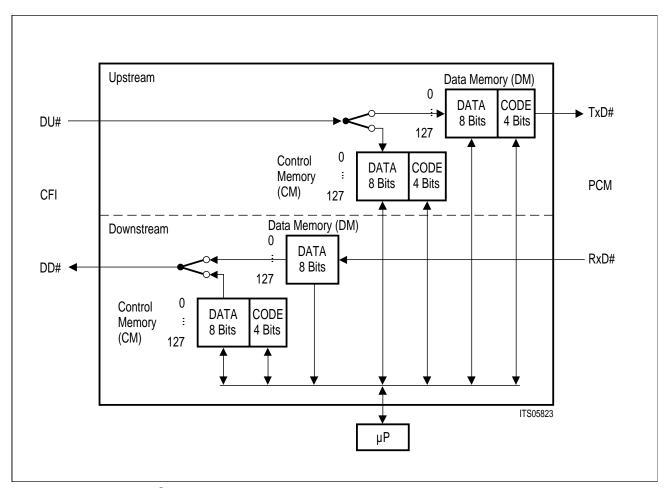

| Figure 2-1   | EPIC®-1 Memory Structure                                             | 2-5    |

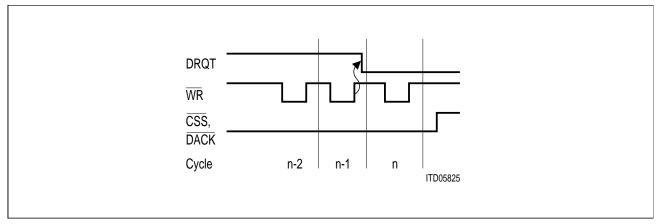

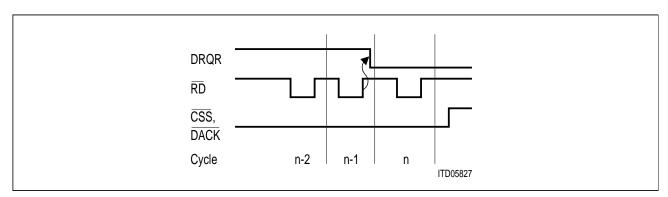

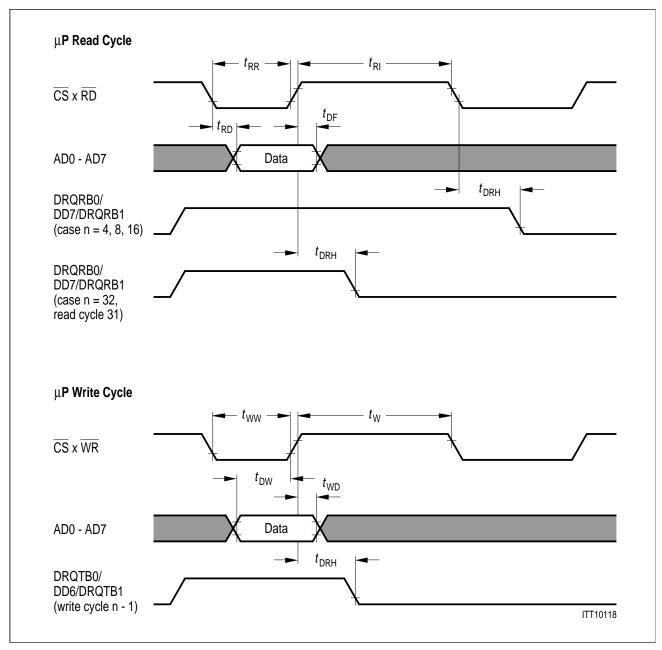

| Figure 2-2   | Timing Diagram for DMA-Transfers (fast) Transmit (n < 32,            |        |

|              | remainder of a long message or $n = k \times 32$ )                   | 2-7    |

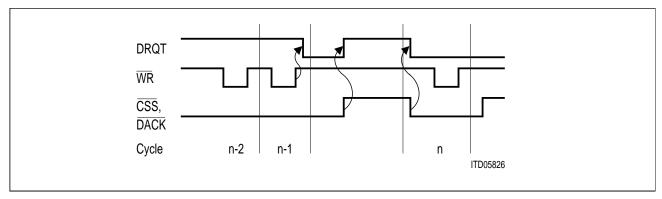

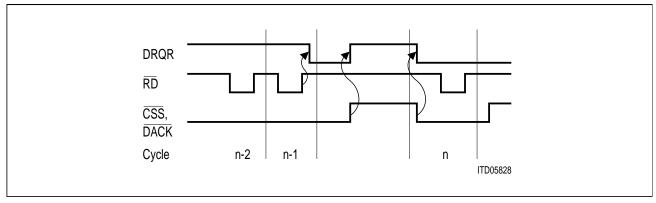

| Figure 2-3   | Timing Diagram for DMA-Transfers (slow) Transmit (n < 32,            |        |

|              | remainder of a long message or $n = k \times 32$ )                   | 2-8    |

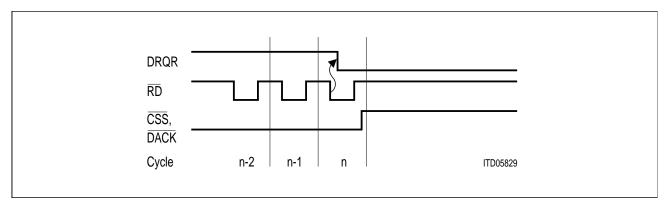

| Figure 2-4   | Timing Diagram for DMA-Transfer (fast) Receive (n = $k \times 32$ )  | 2-8    |

| Figure 2-5   | Timing Diagram for DMA-Transfers (slow) Receive (n = $k \times 32$ ) | 2-8    |

| Figure 2-6   | Timing Diagram for DMA-Transfers (slow or fast) Receive              |        |

|              | (n = 4, 8 or 16)                                                     | 2-9    |

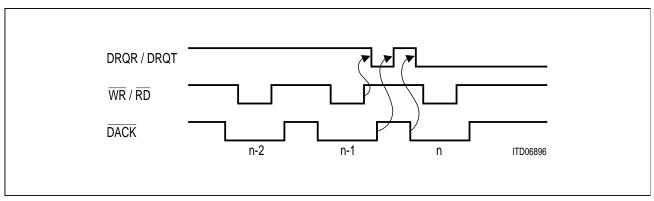

| Figure 2-7   | DMA-Transfers with Pulsed DACK (read or write)                       | 2-9    |

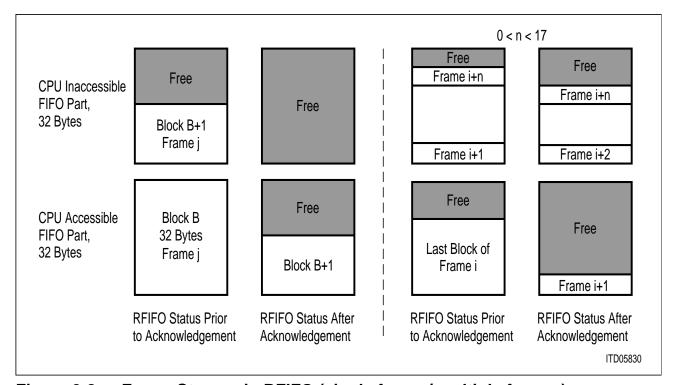

| Figure 2-8   | Frame Storage in RFIFO (single frame / multiple frames)              | . 2-10 |

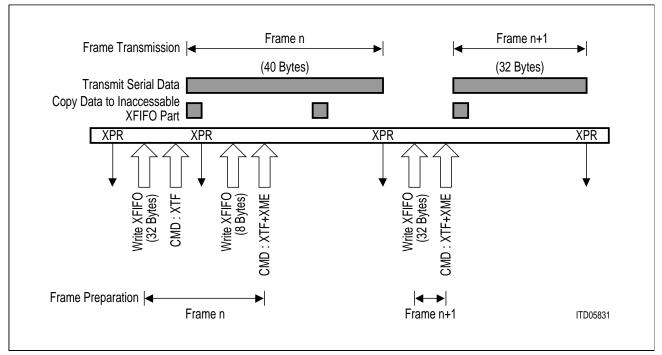

| Figure 2-9   | XFIFO Loading, Continuous Frame Transmission Disabled (CFT = 0       | ) 2-11 |

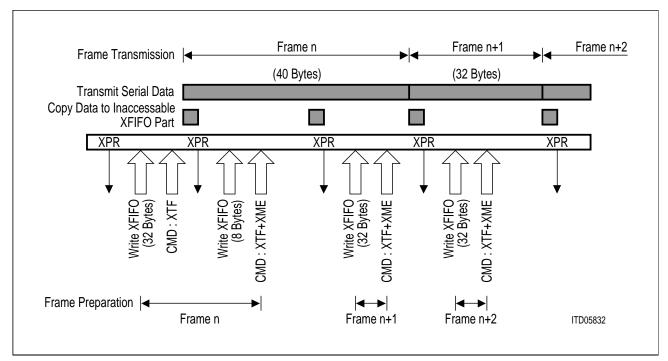

| Figure 2-10  | XFIFO Loading, Continuous Frame Transmission Enabled (CFT = 1        | 2-12   |

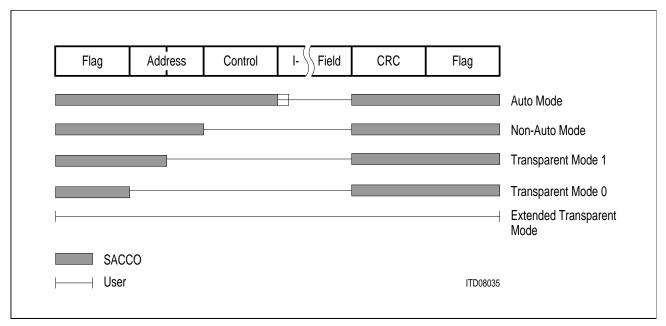

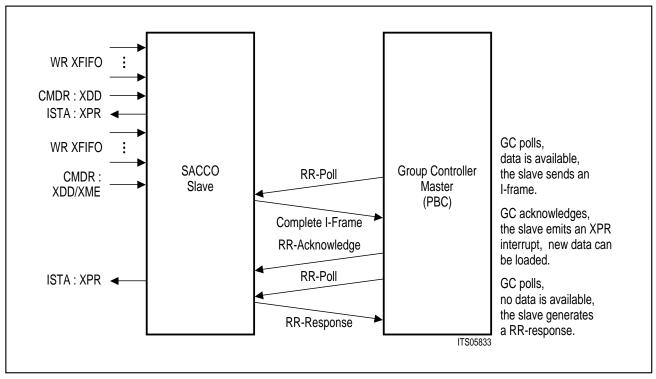

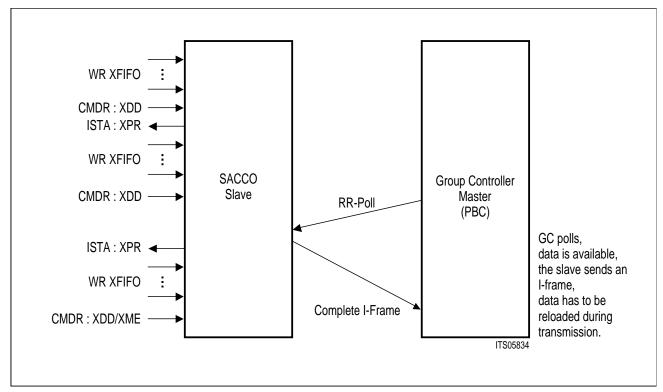

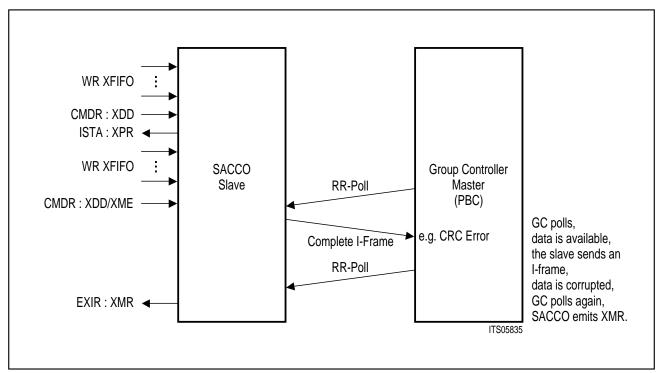

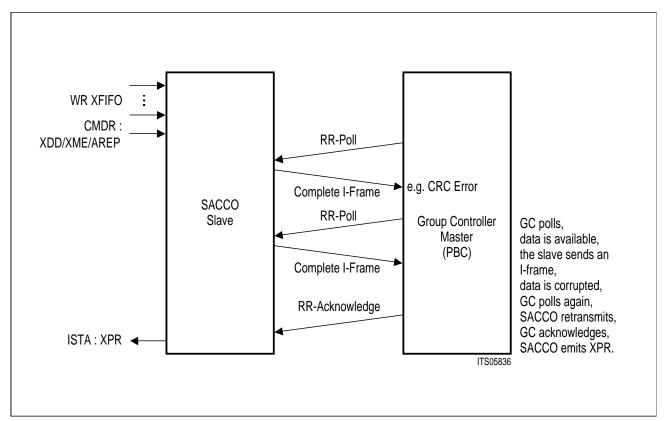

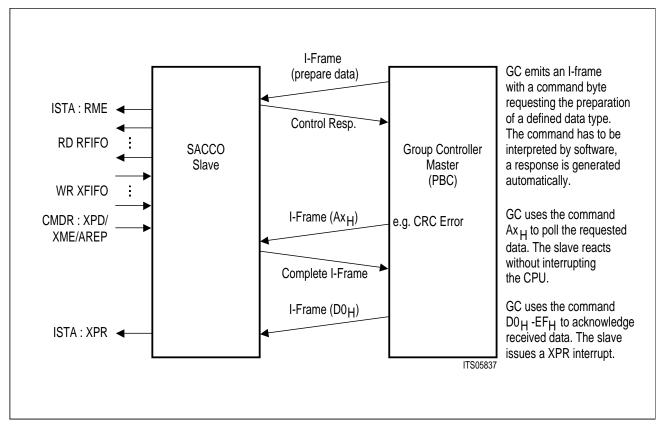

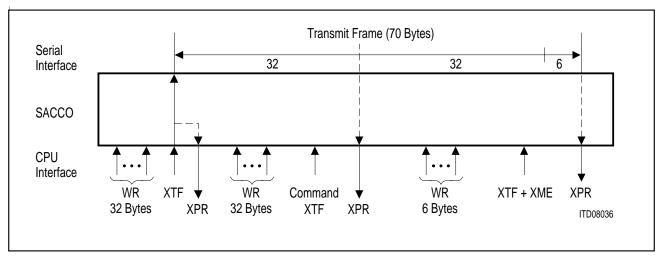

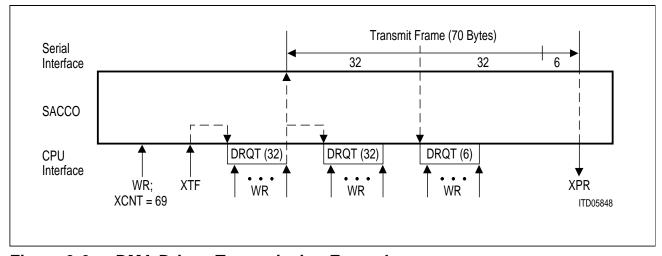

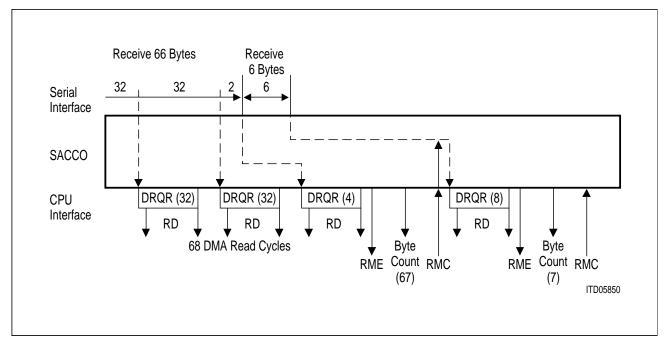

| Figure 2-11  | Support of the HDLC Protocol by the SACCO                            | . 2-13 |

| Figure 2-12  | Polling of up to 64 Bytes Direct Data                                | . 2-19 |

| Figure 2-13  | Polling More than 64 Bytes of Direct Data (e.g. 96 bytes)            | . 2-19 |

| •            | Re-Transmission of a Frame                                           |        |

| •            | Re-Transmission of a Frame with Auto-Repeat Function                 |        |

| Figure 2-16  | Polling of Prepared Data                                             | . 2-22 |

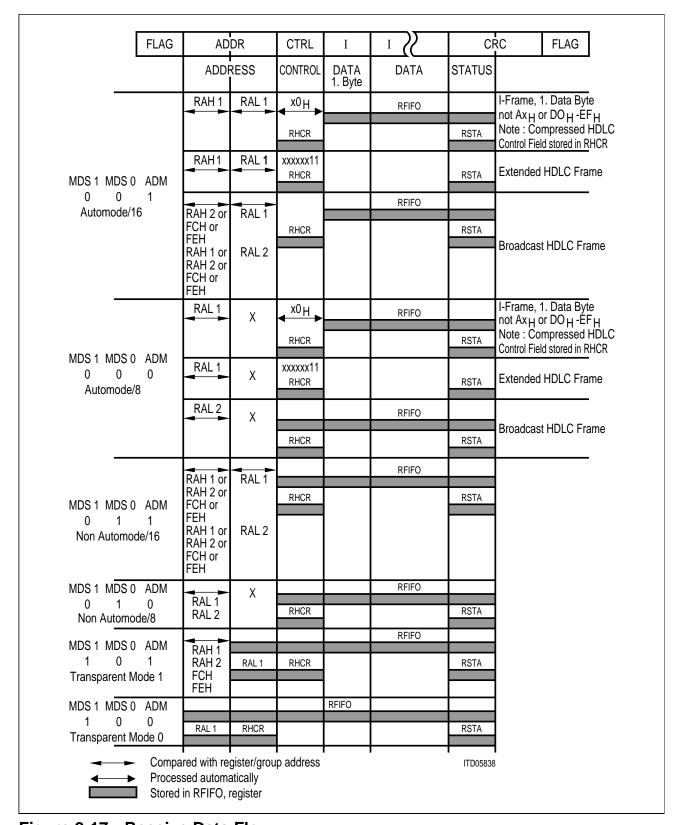

| Figure 2-17  | Receive Data Flow                                                    | . 2-26 |

| •            | Location of Time-Slots                                               |        |

|              | D-Channel Arbiter                                                    |        |

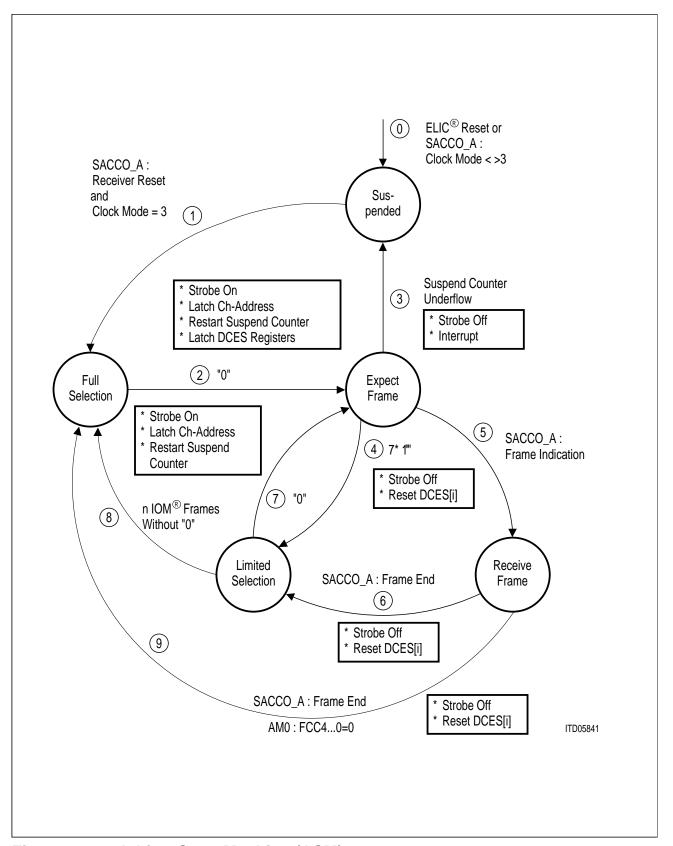

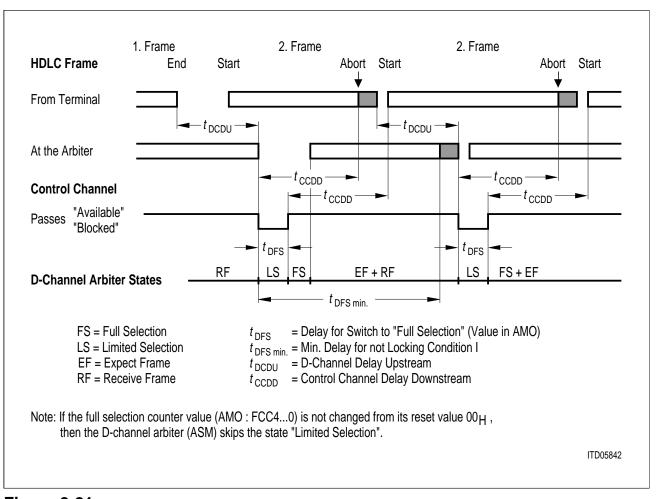

|              | Arbiter State Machine (ASM)                                          |        |

|              |                                                                      |        |

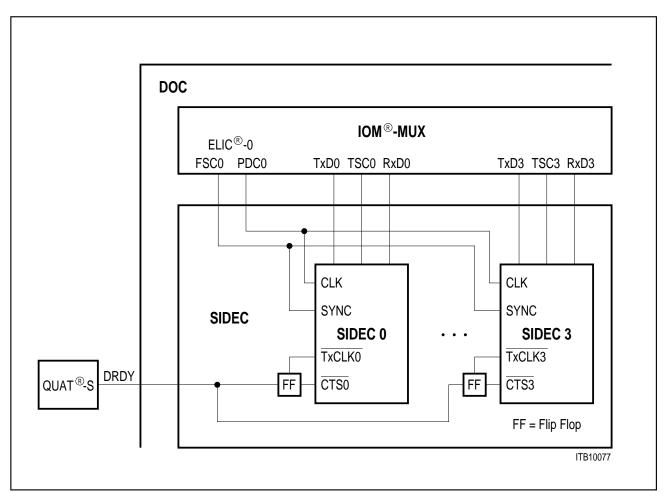

| _            | SIDEC Block Diagram                                                  |        |

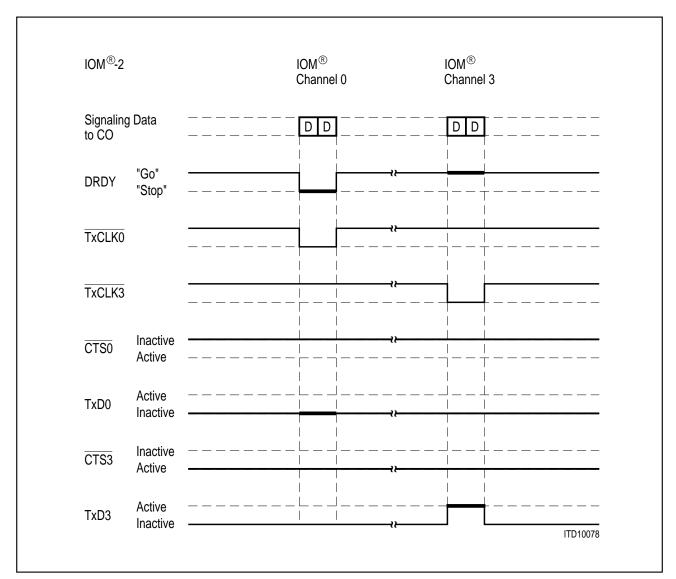

|              | SIDEC Signals                                                        | . 2-42 |

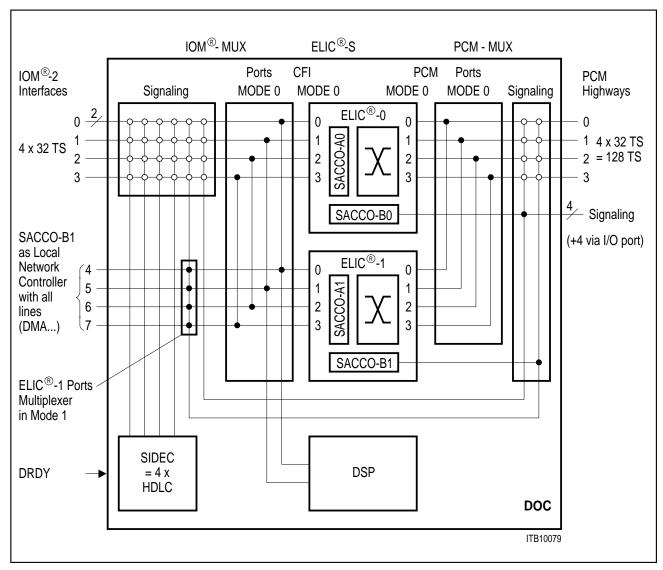

| Figure 2-24  | Principle Block Diagram of IOM and PCM Multiplexers;                 |        |

|              | Mode 0-0-0-1                                                         | . 2-43 |

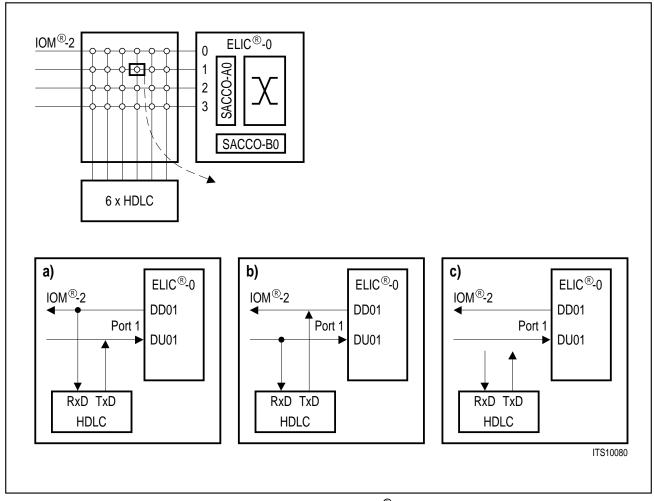

| Figure 2-25  | Modes of HDLC Connection to IOM®-2 Interfaces within the             |        |

|              | Signaling MUX                                                        | . 2-44 |

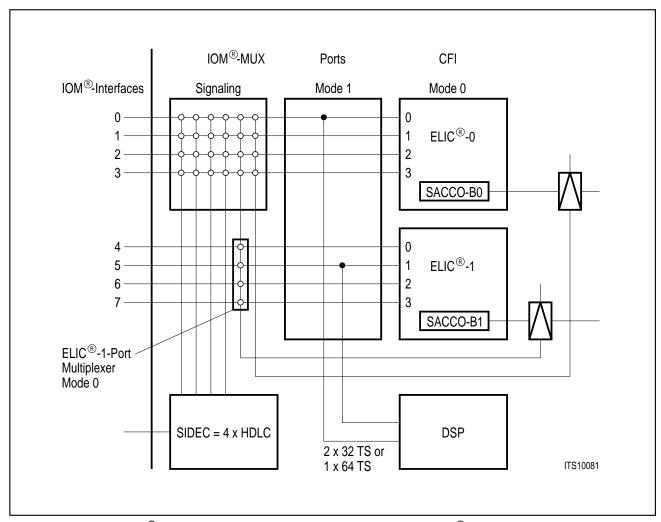

| Figure 2-26  | IOM® Ports Multiplexer in Mode 1 and ELIC®-1-Ports Multiplexer       |        |

|              | in Mode 0                                                            |        |

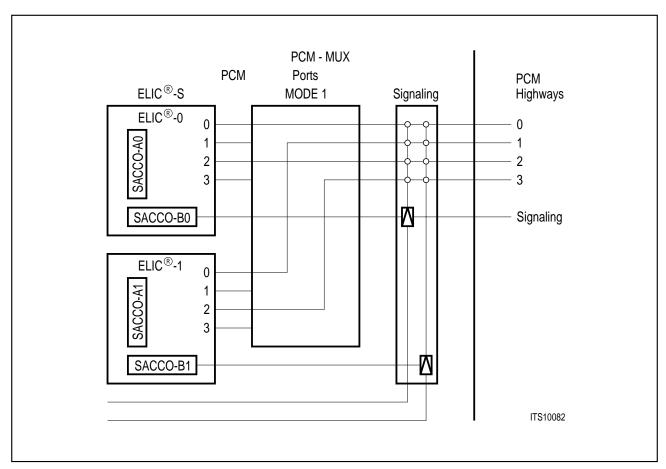

| •            | PCM-Ports Multiplexer in Mode 1                                      |        |

| Figure 2-28  | SACCO-B0 Multiplexers                                                | . 2-48 |

| List of Figu | res                                                              | Page    |

|--------------|------------------------------------------------------------------|---------|

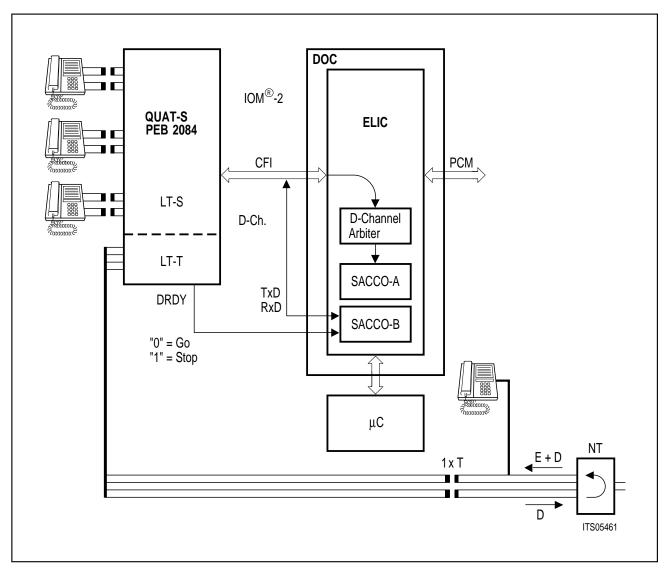

| Figure 2-29  | QUAT-S with SACCO-B for Single-Channel LT-T Application          | 2-49    |

| -            | SACCO-B1 Multiplexers                                            |         |

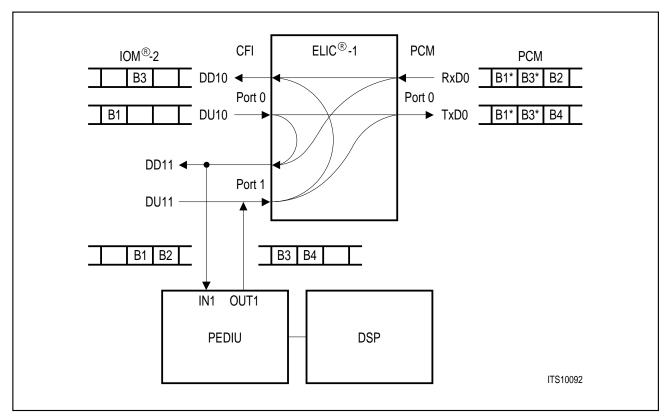

| Figure 2-31  | PEDIU Connection to the ELICs                                    | 2-52    |

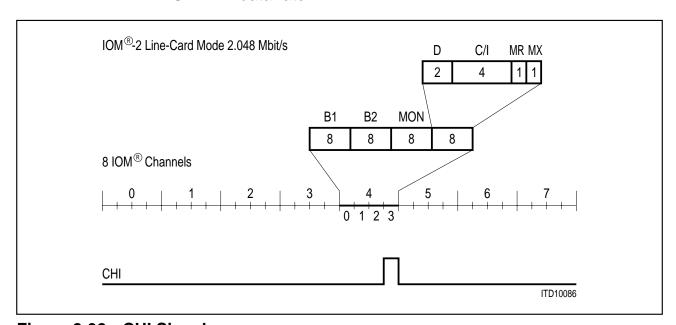

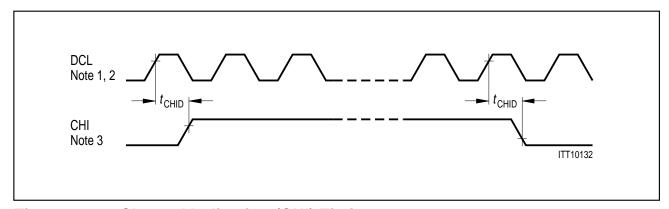

| Figure 2-32  | CHI Signal                                                       | 2-58    |

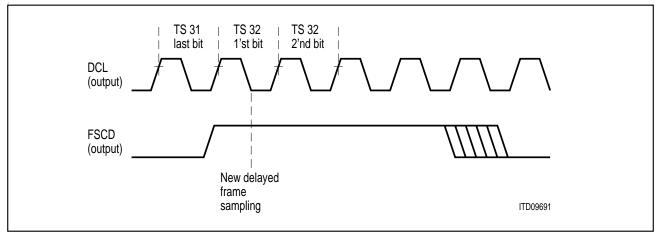

| -            | FSCD Behavior                                                    |         |

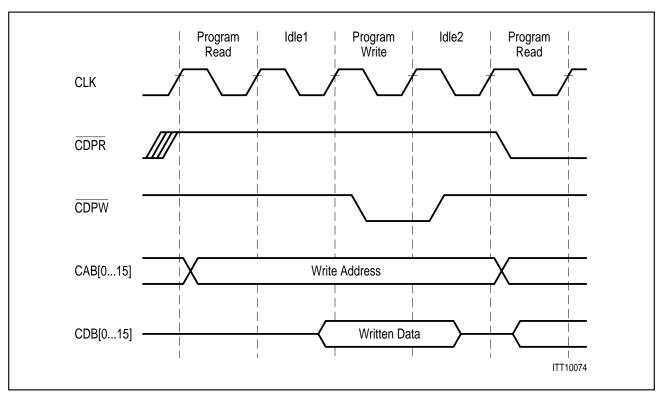

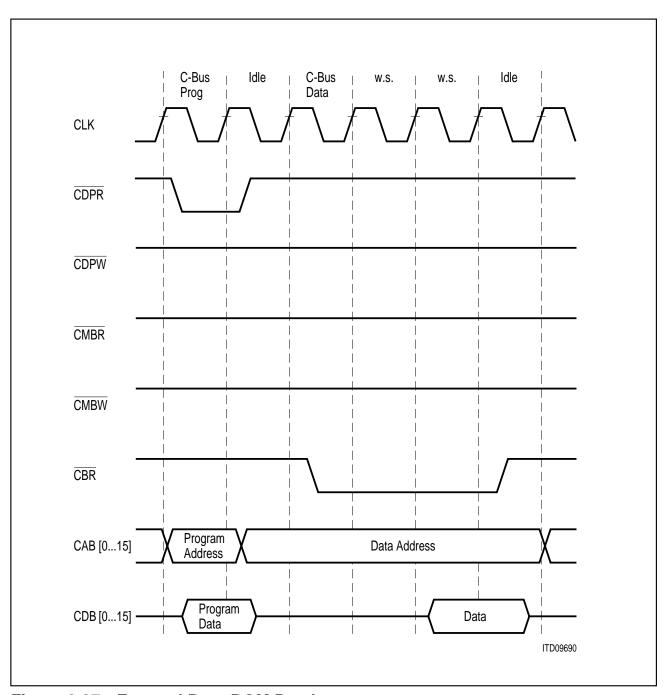

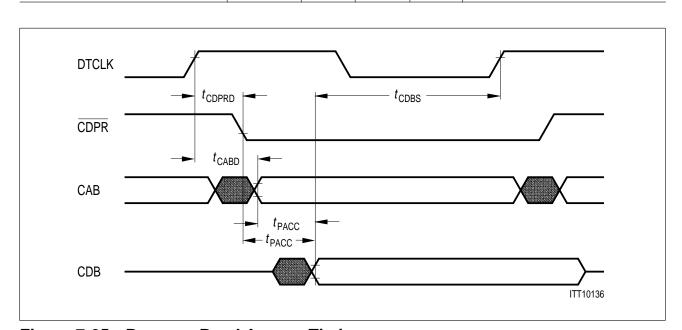

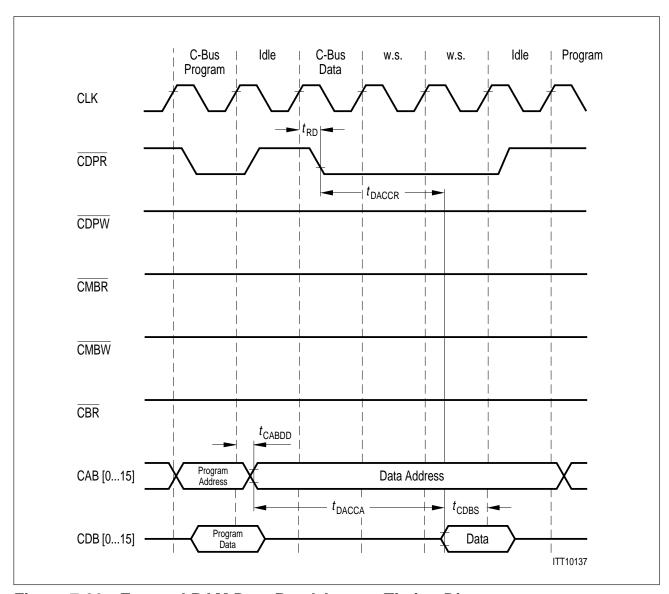

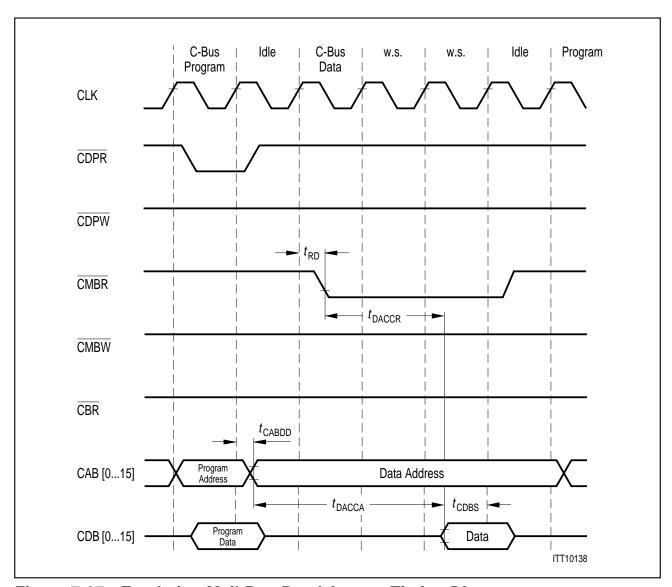

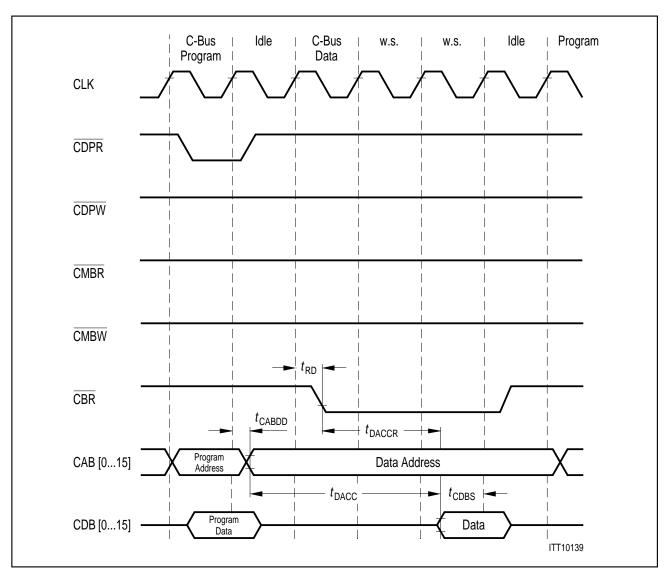

| Figure 2-34  | External Data/Program Read Access                                | 2-64    |

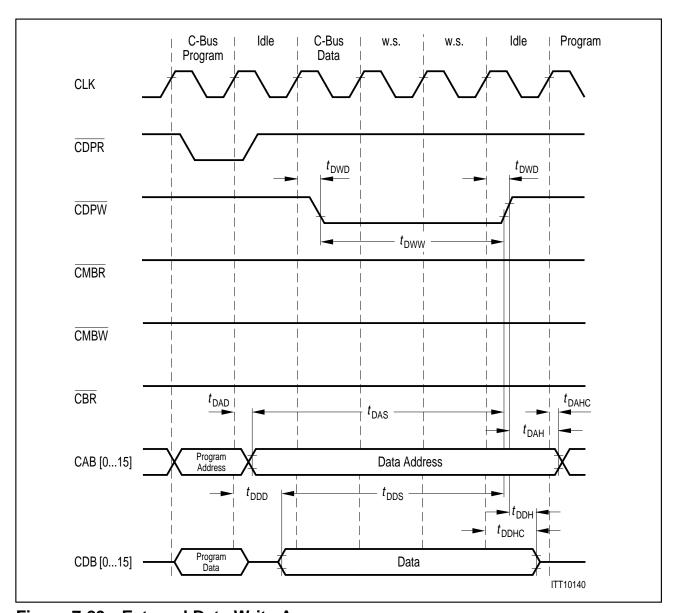

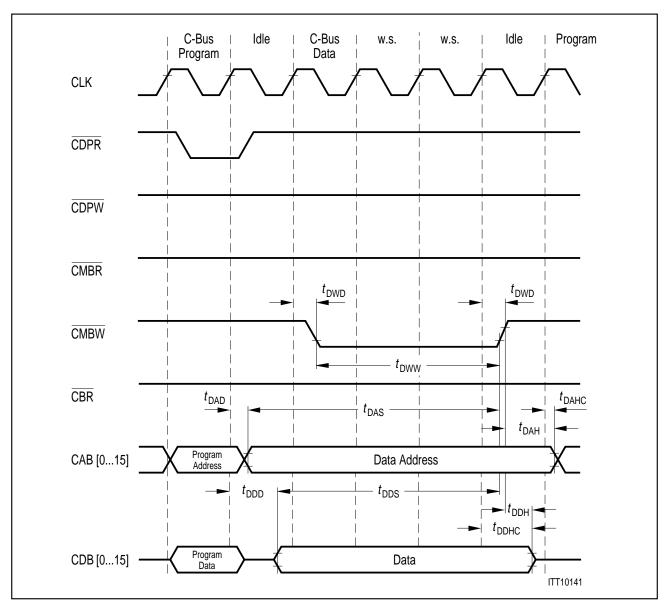

| -            | External Data Write Access                                       |         |

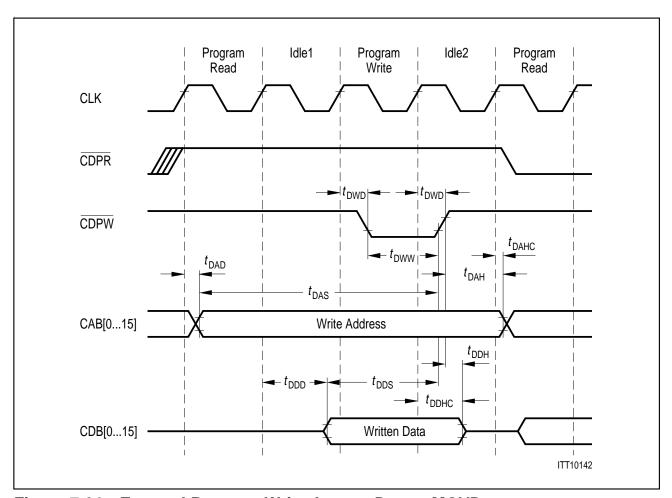

| Figure 2-36  | External Program Write Access Due to MOVD                        | 2-66    |

| Figure 2-37  | External Boot ROM Read                                           | 2-67    |

| Figure 2-38  |                                                                  | 2-71    |

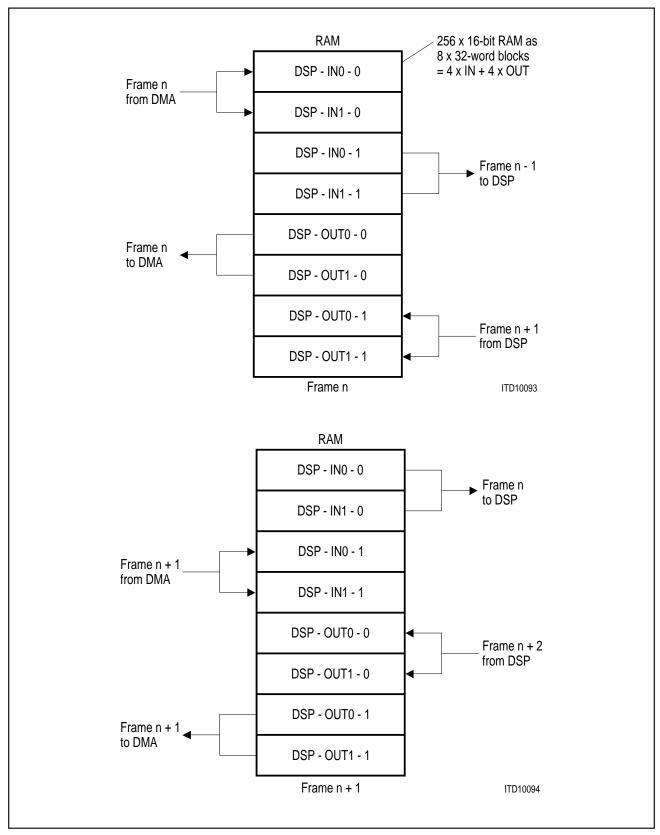

| Figure 2-39  | Example: Flow of B-Channels between ELIC1 and PEDIU              | 2-89    |

| Figure 2-40  | Accesses to the PEDIU RAM (circular buffer) at two               |         |

|              | Consecutive Frames                                               | 2-90    |

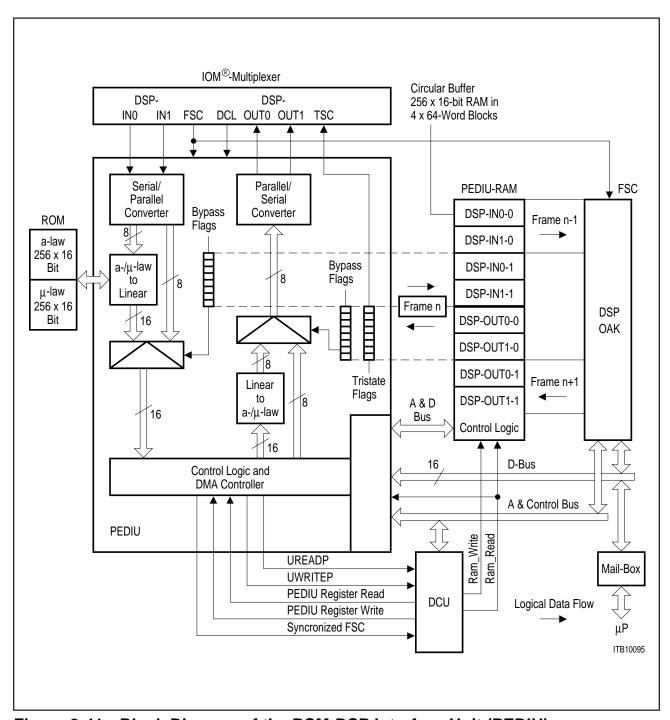

| Figure 2-41  | Block Diagram of the PCM-DSP Interface Unit (PEDIU)              | 2-92    |

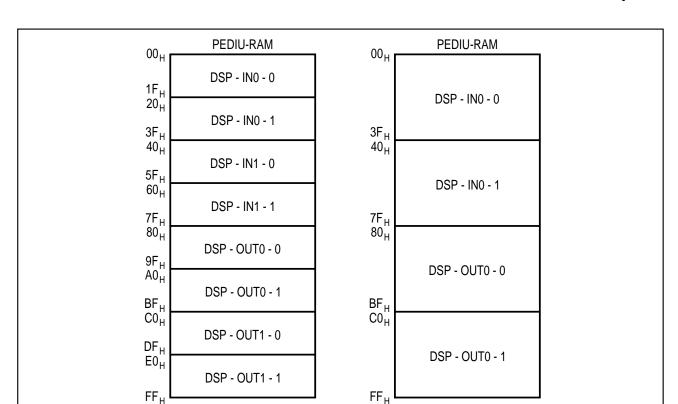

| Figure 2-42  | Block Structure of Circular Buffer (PEDIU RAM) in Different      |         |

|              | PEDIU Work Modes                                                 | 2-96    |

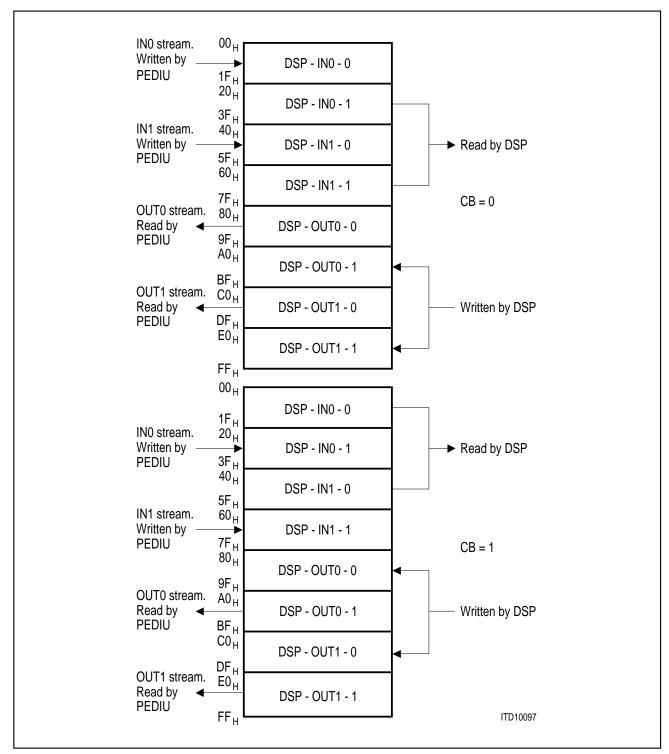

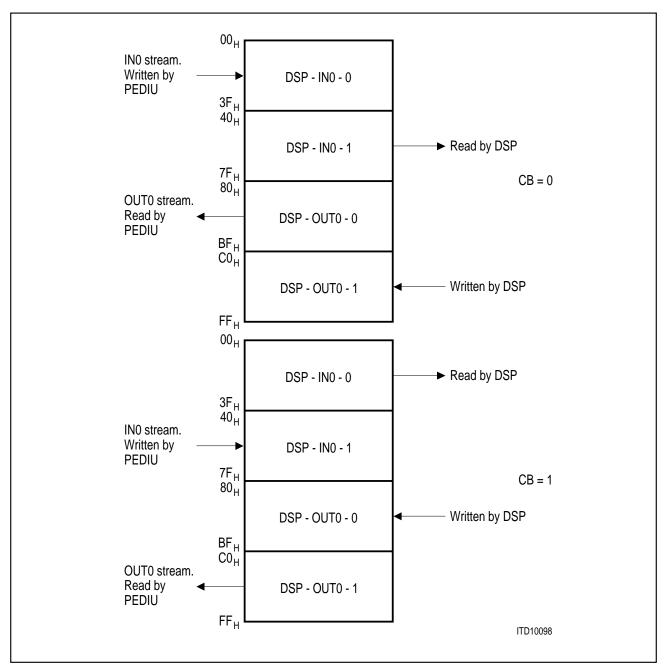

| Figure 2-43  | Connection between CB bit and Accesses to the Circular           |         |

|              | Buffer Blocks in PEDIU work Mode 0, 1 or 2                       | 2-99    |

| Figure 2-44  | The Connection between CB bit and Accesses to the Circular       |         |

|              | Buffer Blocks in PEDIU work Mode 3 or 4                          | . 2-100 |

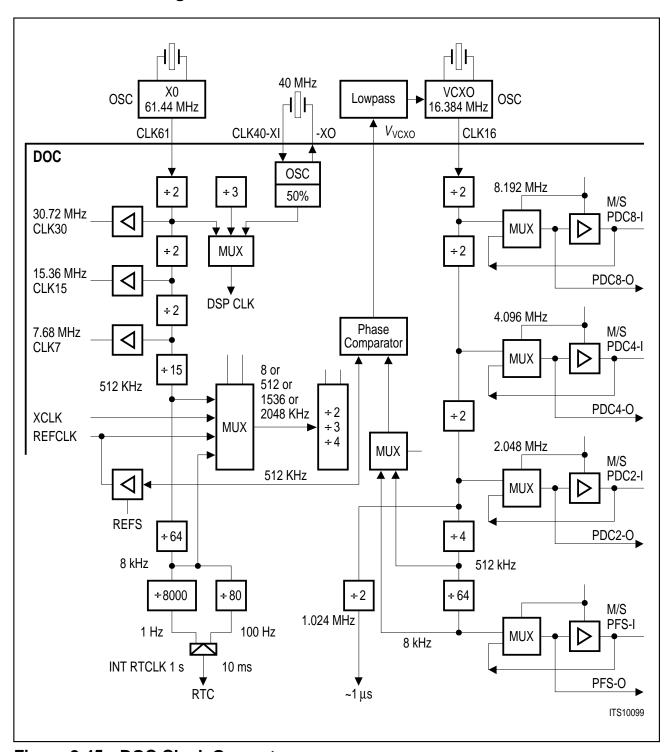

| Figure 2-45  | DOC Clock Generator                                              | . 2-119 |

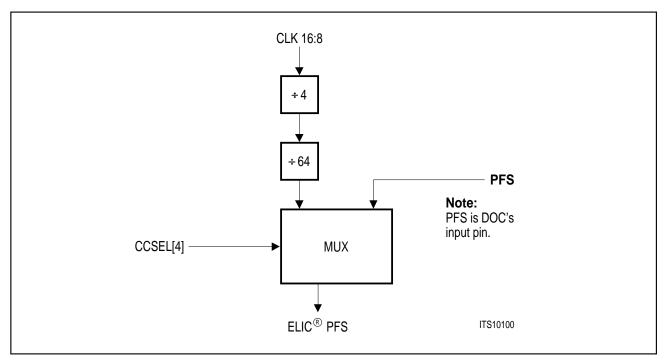

| Figure 2-46  | PFS Signal Selection                                             | . 2-121 |

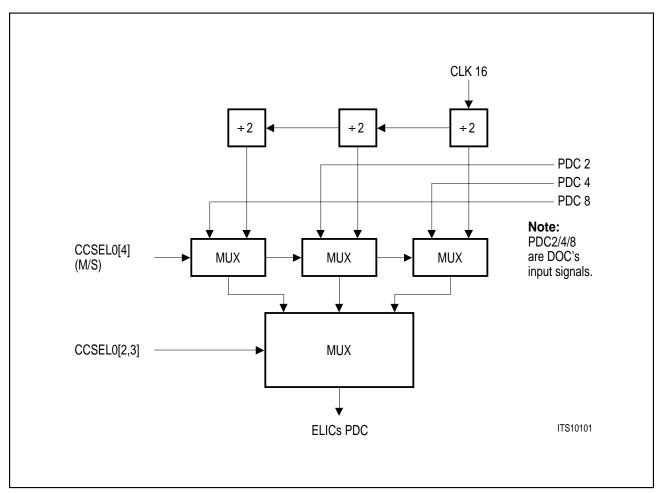

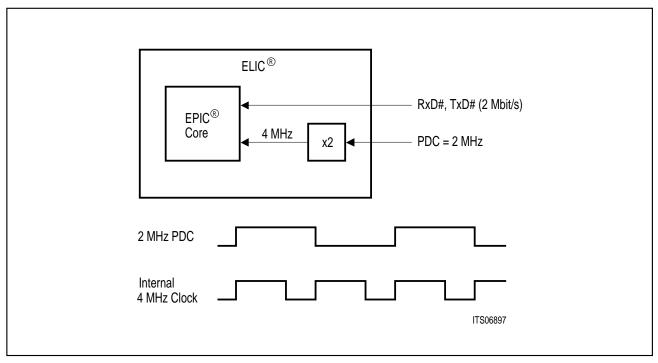

| Figure 2-47  | PDC Generation                                                   | . 2-122 |

| -            | Priority Unit - Block Diagram                                    |         |

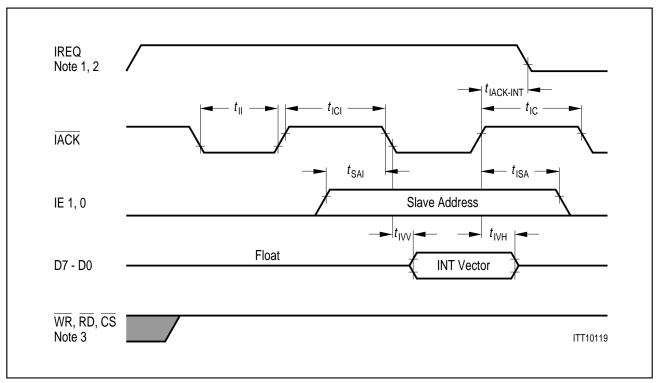

| •            | Interrupt Cascading (Slave Mode) in Siemens/Intel Bus Mode       |         |

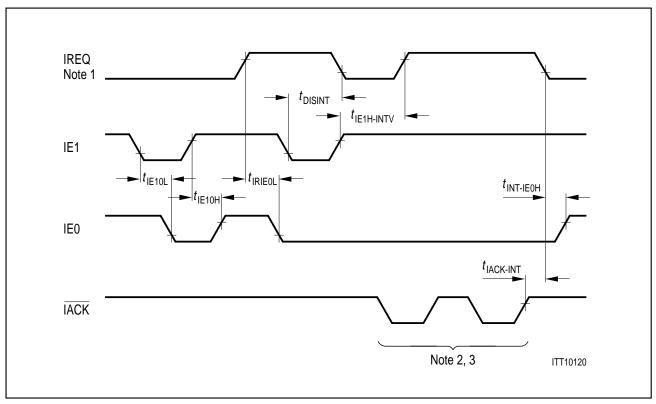

| •            | Interrupt Cascading (Daisy Chaining) in Siemens/Intel Bus Mode . |         |

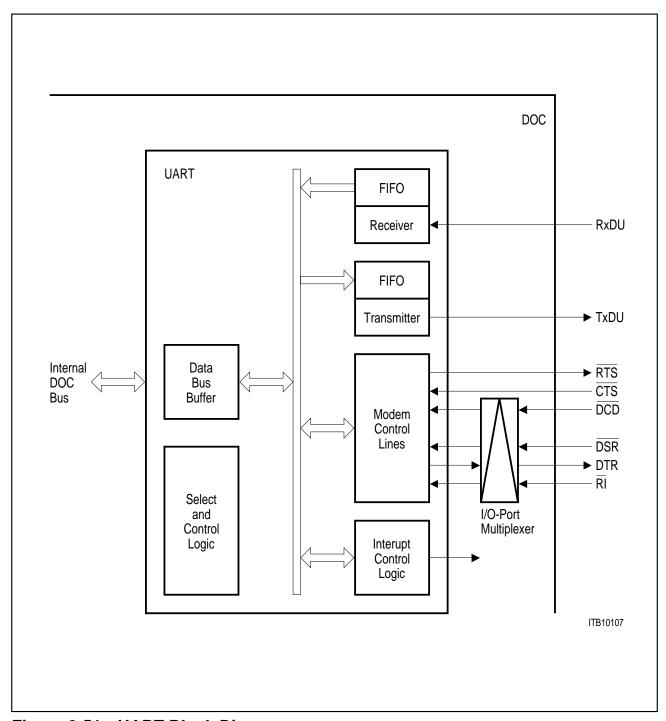

| Figure 2-51  | UART Block Diagram                                               | . 2-138 |

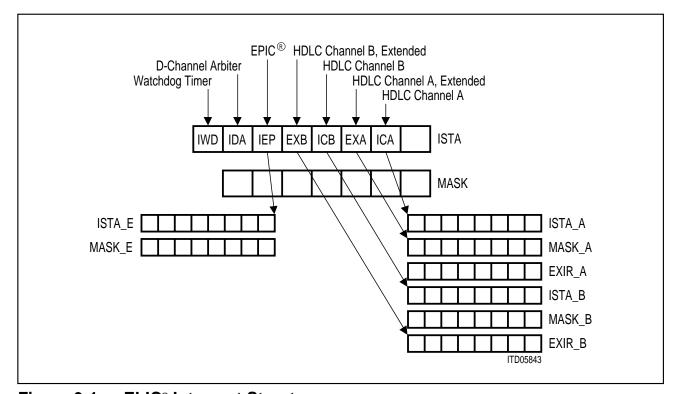

| Figure 3-1   | ELIC® Interrupt Structure                                        | 3-1     |

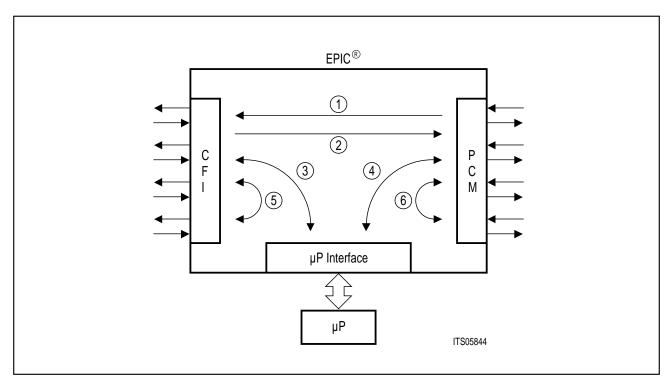

| Figure 3-2   | Switching Paths Inside the EPIC®-1                               |         |

| Figure 3-3   | Pre-Processed Channel Codes                                      |         |

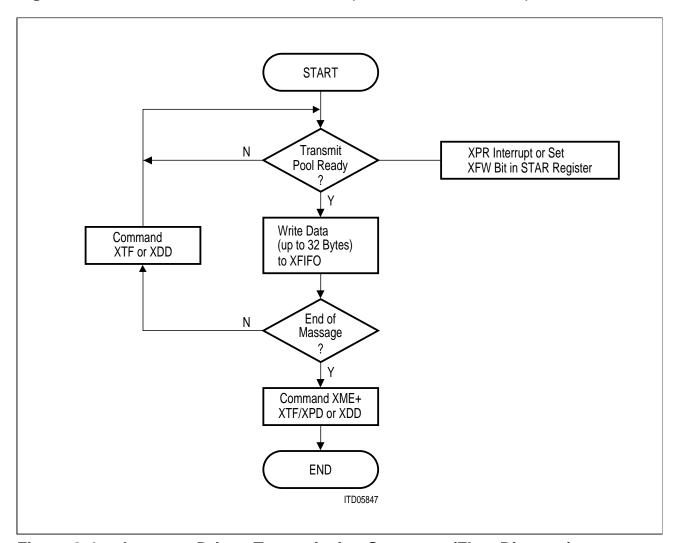

| Figure 3-4   | Interrupt Driven Transmission Sequence (Flow Diagram)            | 3-11    |

| Figure 3-5   | Interrupt Driven Transmission Sequence Example                   |         |

| Figure 3-6   | DMA Driven Transmission Example                                  |         |

| Figure 3-7   | Interrupt Driven Reception Example                               |         |

| Figure 3-8   | DMA-Driven Reception Example                                     |         |

| Figure 3-9   | DOC/ELIC® Interfaces for Initialization Example                  | 3-23    |

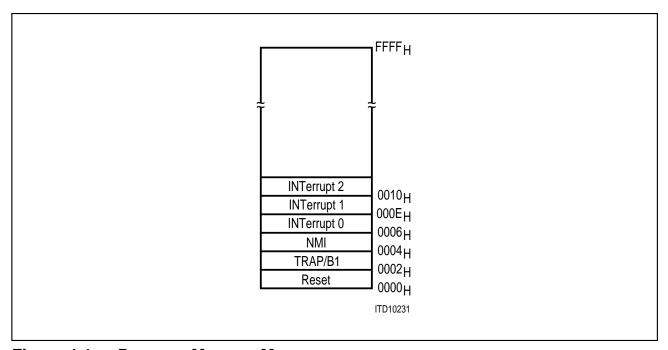

| Figure 4-1   | Program Memory Map                                               |         |

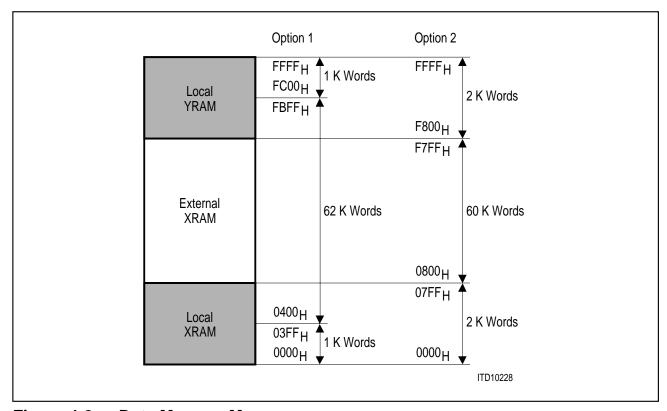

| Figure 4-2   | Data Memory Map                                                  |         |

| Figure 5-1   | Timing Relation Between Internal and External Clock              |         |

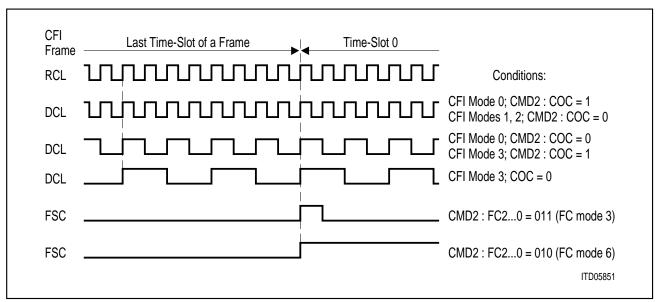

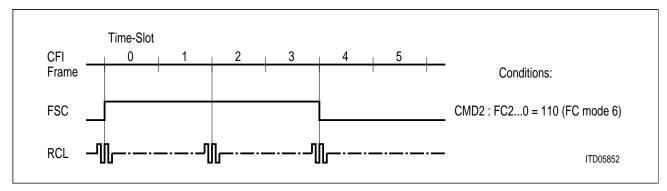

| Figure 5-2   | Position of the FSC-Signal for FC-Modes 3 and 6                  |         |

| Figure 5-3   | Position of the FSC-Signal for FC-Mode 6                         | 5-33    |

| List of Figu | res                                                           | Page   |

|--------------|---------------------------------------------------------------|--------|

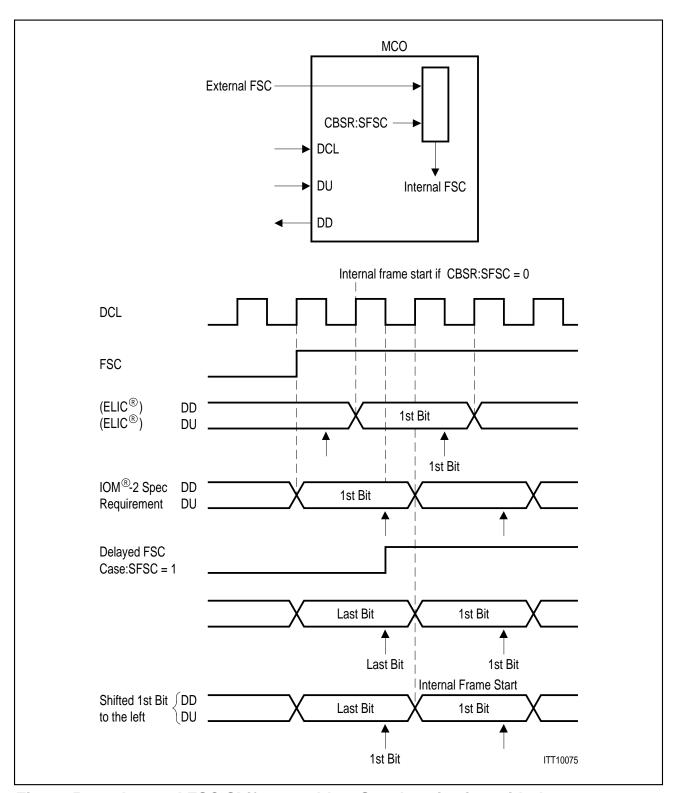

| Figure 5-4   | Internal FSC Shift to enable a Synchronization with the       |        |

|              | Rising Edge of DCL                                            |        |

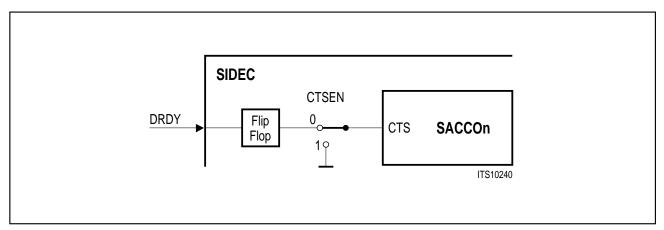

| Figure 5-5   | Use of CTS Signal in SIDEC                                    | . 5-99 |

| Figure 6-1   | DOC in a Small PBX with 2.048 Mbit/s Data Rate                | 6-2    |

| Figure 6-2   | DOC in a Small PBX with 4.096 Mbit/s Data Rate                | 6-3    |

| Figure 6-3   | DOC on Line Card with 2.048 and 4.096 Mbit/s Data Rates       | 6-4    |

| Figure 6-4   | DOC on Line Card with 4.096 and 8.192 Mbit/s Data Rates       | 6-5    |

| Figure 6-5   | Clock Generation in a PBX with one DOC                        | 6-6    |

| Figure 6-6   | Clock Synchronization in a PBX with Multiple DOCs             | 6-7    |

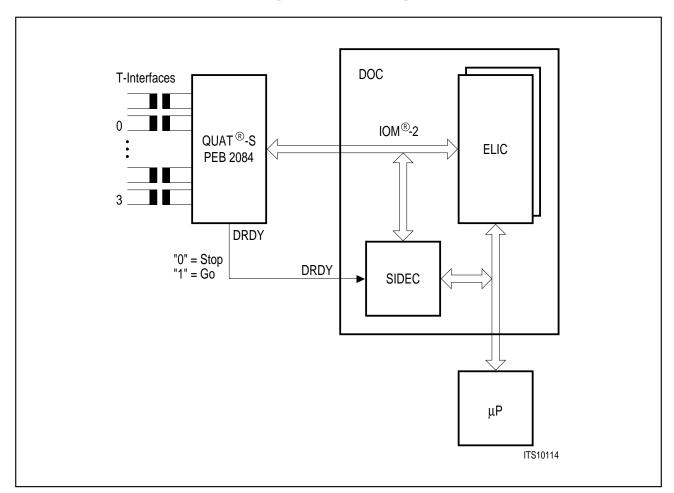

| Figure 6-7   | QUAT-S in LT-T Mode with SIDEC for Four-Channel Trunk         |        |

| _            | Applications                                                  | 6-8    |

| Figure 7-1   |                                                               | 7-4    |

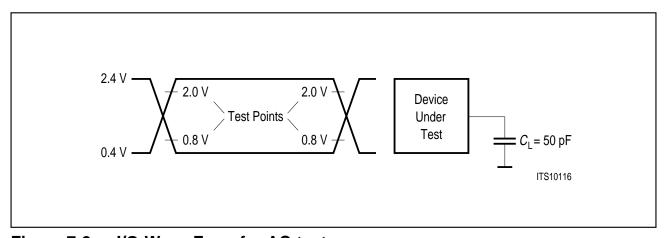

| Figure 7-2   | I/O-Wave Form for AC-test                                     | 7-4    |

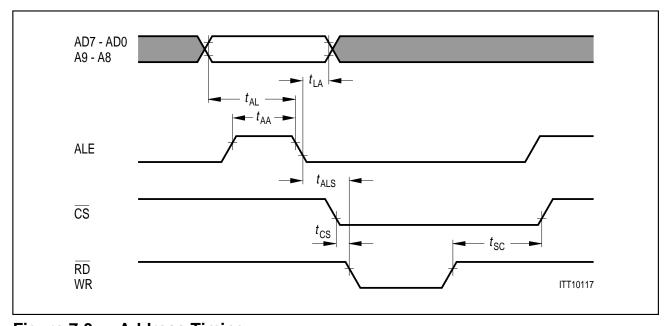

| Figure 7-3   | Address Timing                                                | 7-5    |

| Figure 7-4   | Data Timing                                                   |        |

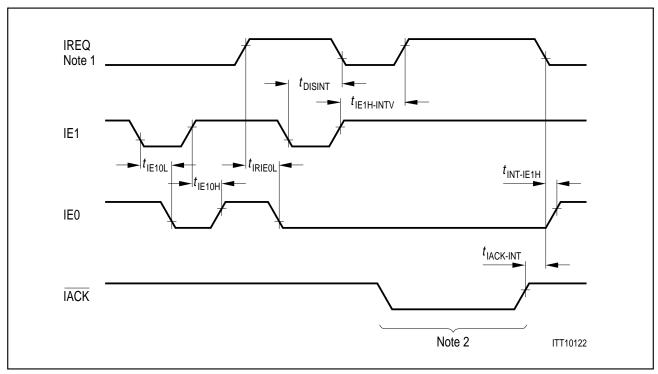

| Figure 7-5   | Siemens/Intel Interrupt Timing (Slave mode)                   |        |

| Figure 7-6   | Siemens/Intel Interrupt Timing (Daisy chaining)               |        |

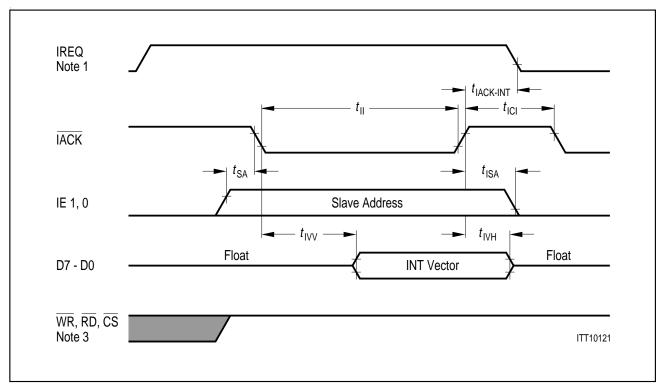

| Figure 7-7   | Motorola Interrupt Timing (Slave mode)                        |        |

| Figure 7-8   | Motorola Interrupt Timing (Daisy chaining)                    |        |

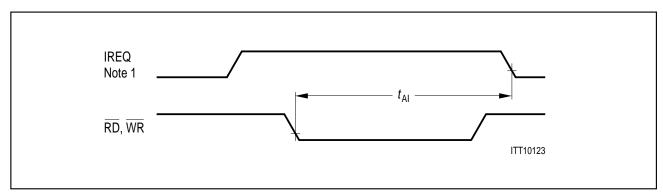

| Figure 7-9   | Interrupt inactivation from WR, RD                            |        |

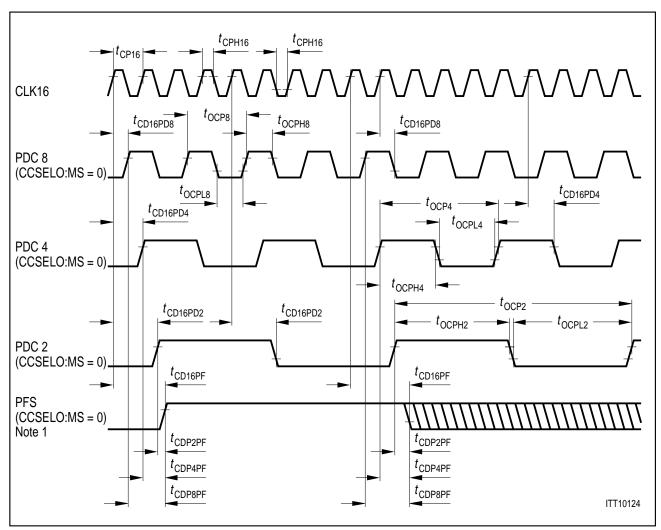

| •            | PDC and PFS Timing In Master Mode (PDC & PFS are outputs)     |        |

| -            | PCM-Interface Timing in Master Mode                           |        |

| •            | PCM-Interface Timing in Slave Mode                            |        |

|              | IOM®-2 Interface Clocks Timing When FSC and DCL are Driven by |        |

| C            | ELIC0 and the DOC is in Slave Mode                            | . 7-21 |

| Figure 7-14  | IOM®-2 Interface Clocks Timing When FSC and DCL are Driven    |        |

| C            | directly by PDC4/8 and PFS, and the DOC is in Slave Mode      | . 7-22 |

| Figure 7-15  | IOM®-2 Interface Clocks Timing when FSC and DCL are Driven    |        |

| C            | Directly by PDC4/8 and PFS, and the DOC is in Master Mode     |        |

|              | (PDC and PFS are generated by internal clocks generator)      | . 7-24 |

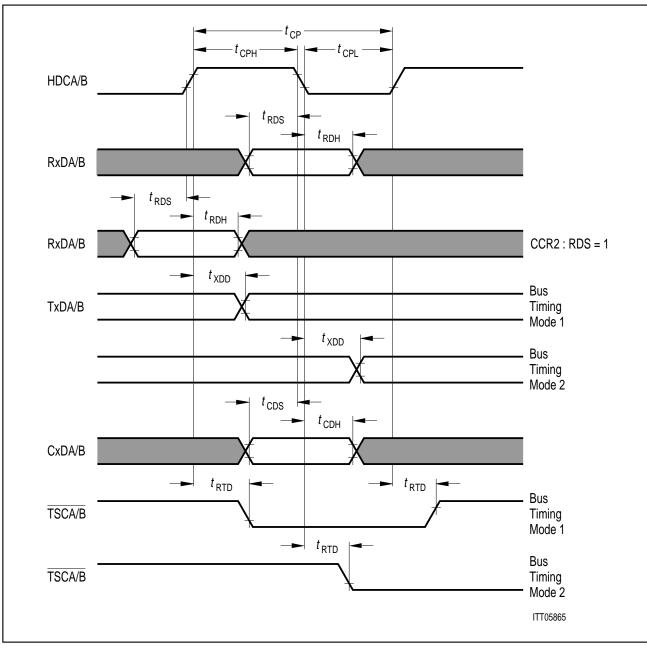

| Figure 7-16  | IOM®-2 Interface Timing                                       |        |

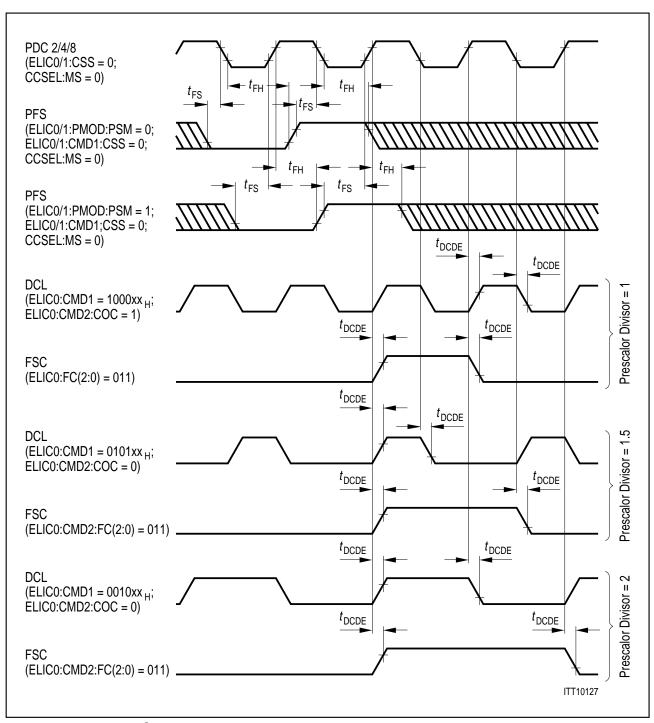

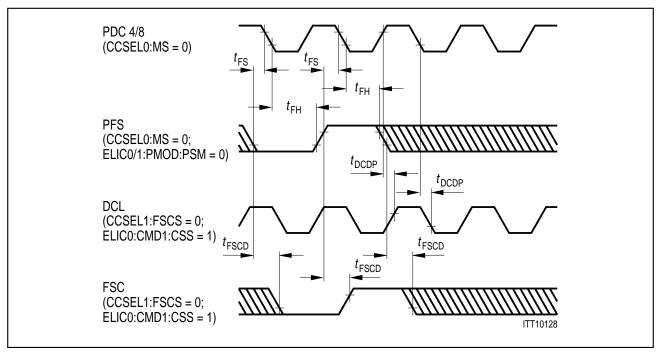

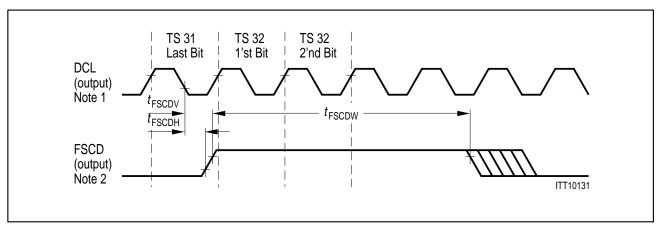

|              | FSCD timing                                                   |        |

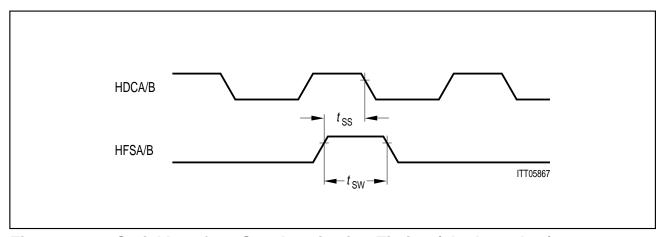

|              | Channel Indication (CHI) Timing                               |        |

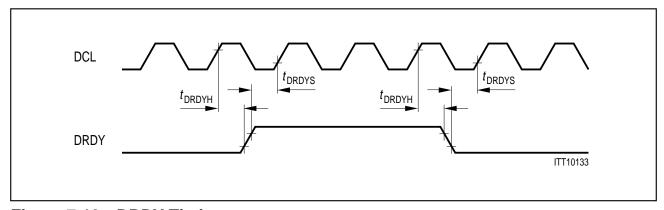

| -            | DRDY Timing                                                   |        |

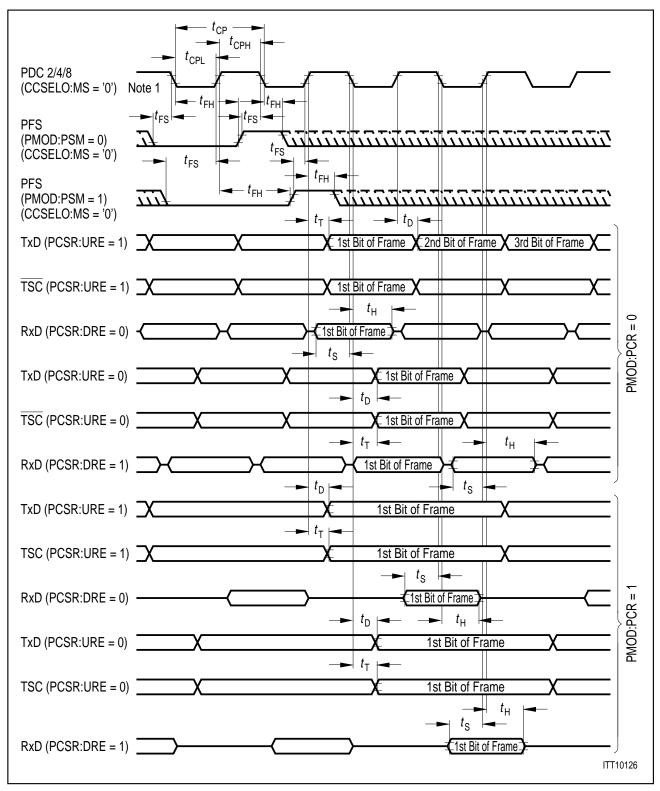

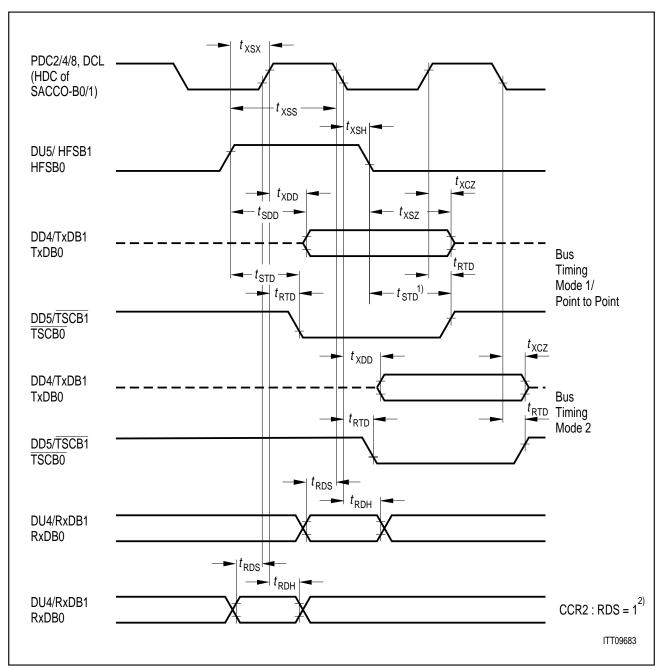

|              | Serial Interface Timing                                       |        |

|              | Serial Interface Strobe Timing (clock mode 1)                 |        |

| •            | Serial Interface Synchronization Timing (clock mode 2)        |        |

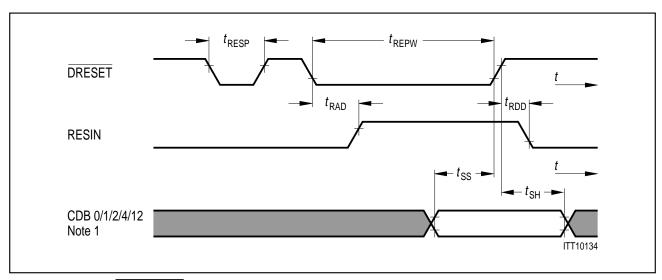

|              | DRESET and RESIN timing                                       |        |

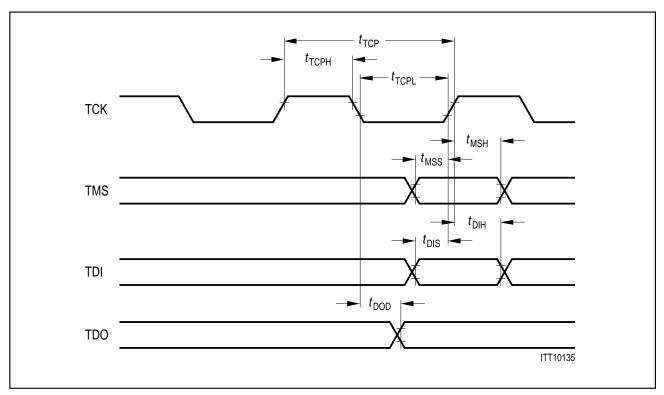

| •            | Boundary Scan Timing                                          |        |

| -            | Program Read Access Timing                                    |        |

| •            | External RAM Data Read Access Timing Diagram                  |        |

| •            | Emulation Mail-Box Read Access Timing Diagram                 |        |

| List of Figu | res                                                              | Page   |

|--------------|------------------------------------------------------------------|--------|

| Figure 7-28  | Boot ROM Read Access Timing Diagram                              | . 7-41 |

|              | External Data Write Access                                       |        |

| Figure 7-30  | Emulation Mail-Box Write Access                                  | . 7-44 |

| Figure 7-31  | External Program Write Access Due to MOVD                        | . 7-45 |

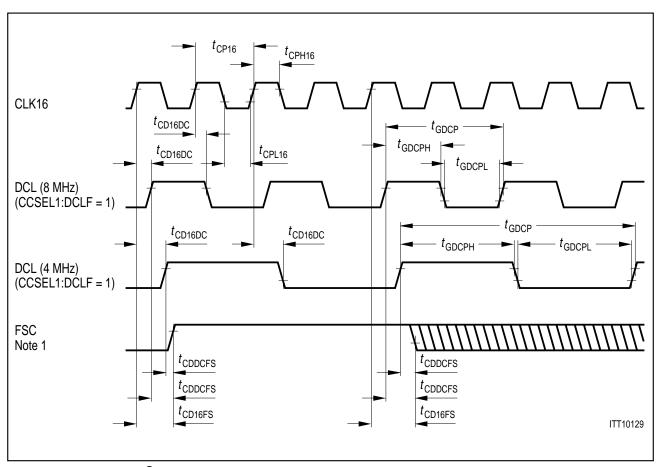

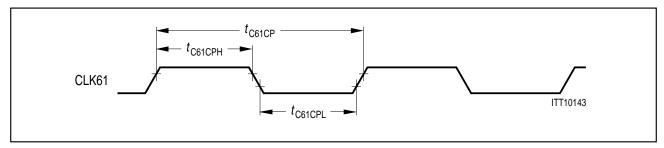

| Figure 7-32  | CLK61 (input) Timing                                             | . 7-46 |

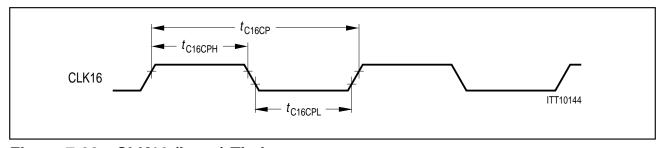

| Figure 7-33  | CLK16 (input) Timing                                             | . 7-46 |

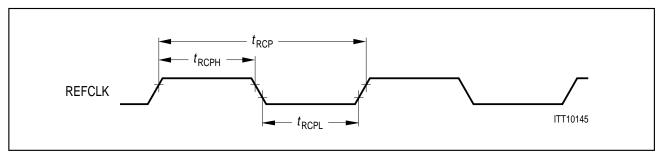

| Figure 7-34  | REFCLK Timing                                                    | . 7-47 |

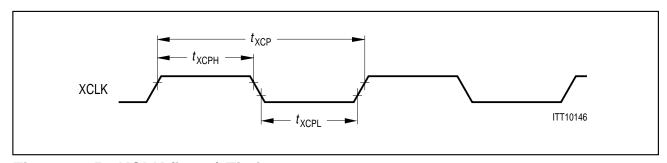

| Figure 7-35  | XCLK (input) Timing                                              | . 7-47 |

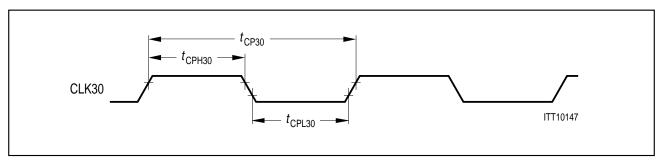

| Figure 7-36  | CLK30 (output) Timing                                            | . 7-48 |

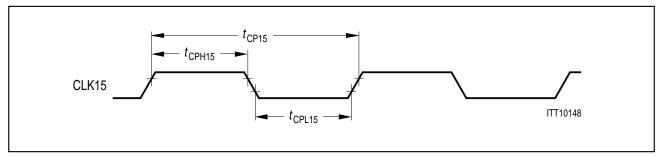

| Figure 7-37  | CLK15 (output) Timing                                            | . 7-48 |

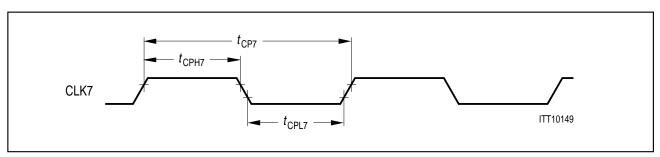

| Figure 7-38  | CLK7 (output) Timing                                             | . 7-49 |

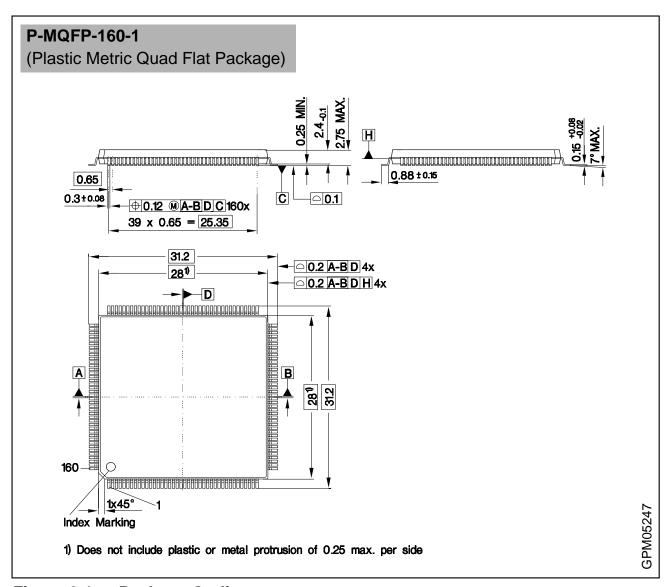

| Figure 8-1   | Package Outline                                                  | 8-1    |

| Figure 9-1   | IOM®-2 Interface with 4-bit C/I Channel                          | 9-1    |

| Figure 9-2   | IOM®-2 Interface Timing with Single Data Rate DCL                | 9-2    |

|              | Timing of the IOM®-2 Interface with Double Data Rate DCL         |        |

| Figure 9-4 a | EPIC® Initialization Register Summary (working sheet)            | 9-5    |

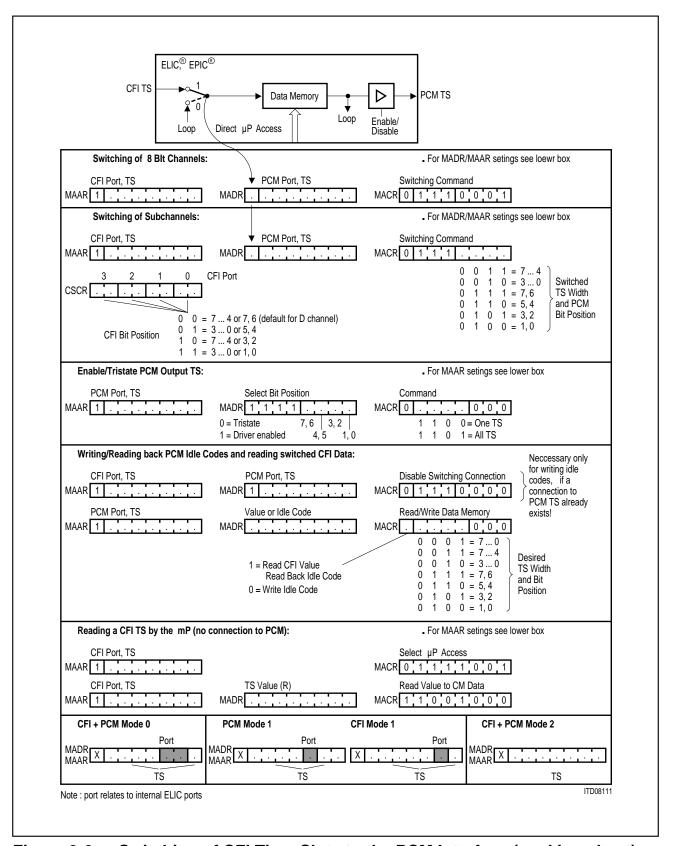

| Figure 9-4 b | Switching of PCM Time-Slots to the CFI Interface (working sheet) | 9-9    |

|              | Switching of CFI Time-Slots to the PCM Interface (working sheet) |        |

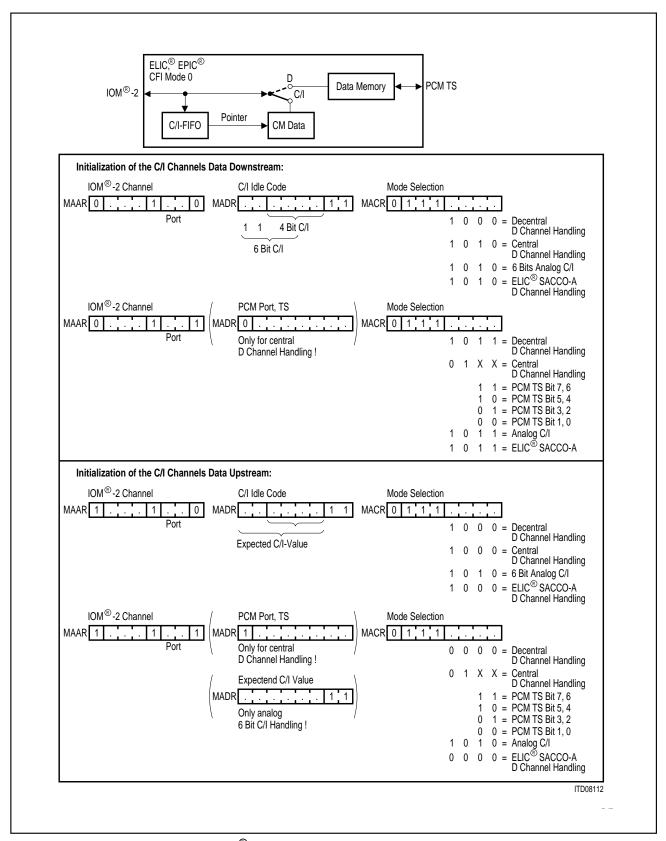

| Figure 9-4 d | Preparing EPIC®s C/I Channels (working sheet)                    |        |

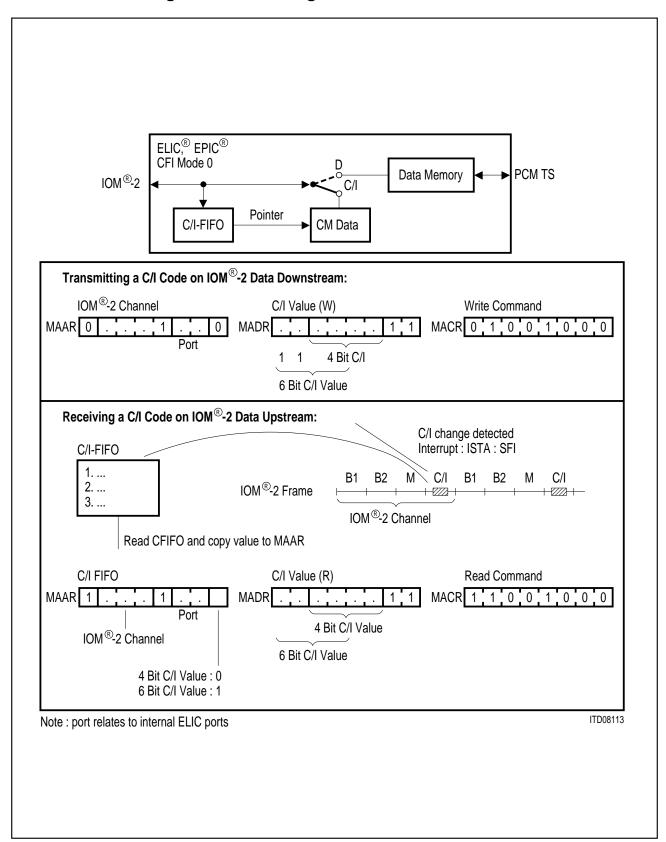

| Figure 9-5   | Receiving and Transmitting IOM®-2 C/I-Codes (working sheet)      | . 9-12 |

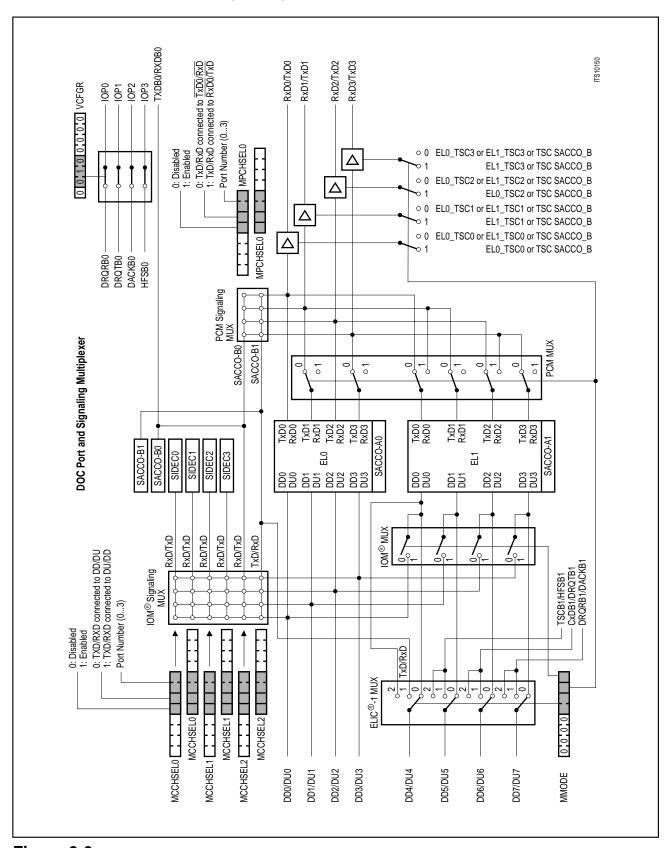

| Figure 9-6   |                                                                  | . 9-13 |

| Figure 9-7   |                                                                  | . 9-14 |

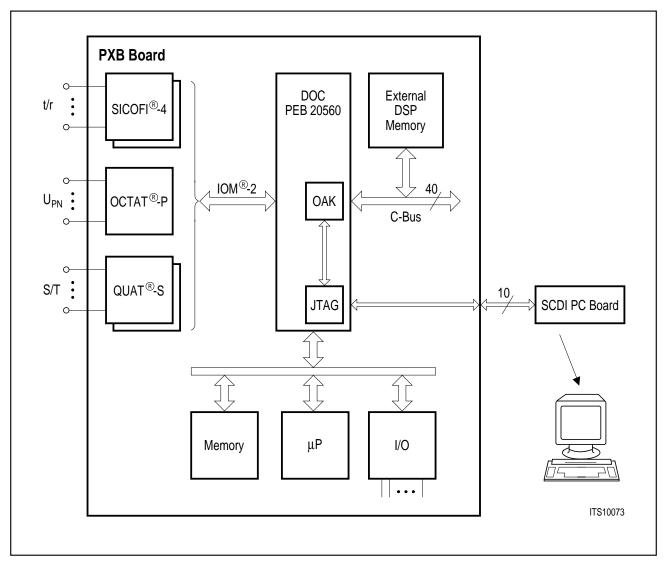

| Figure 9-8   | DOC Evaluation Board - Block Diagram                             | . 9-16 |

| Figure 9-9   | DOC Evaluation System                                            | . 9-17 |

| Figure 9-10  | Example for SIDECs and SACCOs Assignment                         | . 9-18 |

| Figure 9-11  | Example for Selection of ELIC Clocks                             | . 9-19 |

| List of Tab | les                                                              | Page           |

|-------------|------------------------------------------------------------------|----------------|

| Table 1-1   | IOM®-2 Interface                                                 | . 1-9          |

| Table 1-2   | PCM Interface                                                    |                |

| Table 1-3   | Communication and Signaling Interfaces                           |                |

| Table 1-4   | DSP External Memory Interface                                    |                |

| Table 1-5   | Clock Signals (additional to the IOM®-2, PCM and SCC clocks)     |                |

| Table 1-6   | μP Interface                                                     |                |

| Table 1-7   | Input / Output Port                                              |                |

| Table 1-8   | Power Supply                                                     |                |

| Table 1-9   | Test and Emulation Interfaces                                    |                |

| Table 2-1   | Watchdog Timer Programming                                       |                |

| Table 2-2   | Reset Activities                                                 |                |

| Table 2-3   | Behavior of the Reset Logic in the Case of Voltage Drop          |                |

| Table 2-4   | Address Recognition                                              |                |

| Table 2-5   | Auto-Mode Data Types                                             |                |

| Table 2-6   | HDLC-Control Field in Auto-Mode                                  |                |

| Table 2-7   | Auto-Mode Command Byte Interpretation                            |                |

| Table 2-8   | Auto-Mode Response Generation                                    |                |

| Table 2-9   |                                                                  |                |

| Table 2-10  | Control Channel Implementation                                   |                |

| Table 2-11  |                                                                  |                |

| Table 2-12  | Control Channel Delay Examples                                   |                |

| Table 2-13  |                                                                  |                |

| Table 2-14  |                                                                  |                |

| Table 2-15  | DSP Program Address Space                                        |                |

| Table 2-16  | DSP Data Address Space                                           |                |

| Table 2-17  | Interrupt Map                                                    |                |

| Table 2-18  | Boot Mode                                                        | . 2-74         |

| Table 2-19  |                                                                  | . 2-75         |

| Table 2-20  | EPROM/ROM Data Structure                                         | 2-76           |

| Table 2-21  | Work Modes Specifications of the PEDIU                           | . 2-94         |

| Table 2-22  | Address Spaces of Circular Buffer Blocks as a Function           |                |

| Table 2.22  | of the PEDIU Work Mode                                           | 2-90           |

| Table 2-23  | · · · · · · · · · · · · · · · · · · ·                            | 2 101          |

| Table 2.24  | in UISB-PER, in the Different Work Modes of the PEDIU            | . 2-101        |

| Table 2-24  |                                                                  | 2 104          |

| Table 2.25  | Each Bit in UOSBPER, in the Different Work Modes of the PEDIU.   | . 2-104        |

| Table 2-25  | Specification of the Time-Slot Quadruplet Controlled by Each Bit | 0.405          |

| Table 0.00  | in UOSB-PER, in the Different Work Modes of the PEDIU            |                |

| Table 2-26  | PEDIU Registers Addresses in the DSP Address Space               |                |

| Table 2-27  | Register Contents                                                |                |

| Table 2-28  | Interrupt Sources                                                | 2-130<br>2-133 |

| 12018 7-79  |                                                                  | 7-1.55         |

| List of Tab | les                                      | Page    |

|-------------|------------------------------------------|---------|

| Table 2-30  |                                          | . 2-135 |

| Table 2-31  | Summary of Registers 1                   |         |

| Table 2-32  | Summary of Registers 2                   |         |

| Table 2-33  | Register Reset Values                    |         |

| Table 2-34  | UART Registers and Addresses             |         |

| Table 2-35  | Baud Rates Using 61.44 MHz Crystal       |         |

| Table 2-36  | IIR Register                             |         |

| Table 2-37  | Boundary Scan Cell Types                 |         |

| Table 2-38  | Instruction Code of 4 Bit TAP Controller |         |

| Table 2-39  | Data Path of 4 Bit TAP Controller        |         |

| Table 3-1   |                                          | 3-14    |

| Table 3-2   | Pre-processed Channel Options at the CFI | 3-18    |

| Table 3-3   | Mode Dependent Register Set-up           |         |

| Table 3-4   | Feature Dependent Register Set-up        |         |

| Table 3-5   | Mode Dependent Register Set-up           |         |

| Table 3-6   | Feature Dependent Register Set-up        |         |

| Table 5-1   | ELICO SACCO-A                            |         |

| Table 5-2   | ELICO SACCO-B                            |         |

| Table 5-3   | ELICO-EPIC                               |         |

| Table 5-4   | ELICO-MODE REGISTER                      | 5-5     |

| Table 5-5   | ELICO-WATCH-DOG TIMER                    |         |

| Table 5-6   | ELICO-INTERRUPT TOP LEVEL                | 5-5     |

| Table 5-7   | ELICO-ARBITER                            |         |

| Table 5-8   | ELIC1 SACCO-A                            | 5-6     |

| Table 5-9   | ELIC1 SACCO-B                            |         |

| Table 5-10  | ELIC1-EPIC                               |         |

| Table 5-11  | ELIC1-MODE REGISTER                      | 5-10    |

| Table 5-12  | ELIC1-INTERRUPT TOP LEVEL                | 5-10    |

| Table 5-13  | ELIC1-ARBITER                            | 5-10    |

| Table 5-14  | SIDEC0                                   | 5-11    |

| Table 5-15  | SIDEC1                                   | 5-12    |

| Table 5-16  | SIDEC2                                   | 5-13    |

| Table 5-17  | SIDEC3                                   | 5-14    |

| Table 5-18  | ICU                                      | 5-15    |

| Table 5-19  | GPIO                                     | 5-15    |

| Table 5-20  | CHI                                      | 5-15    |

| Table 5-21  | OAK MAIL BOX                             | 5-16    |

| Table 5-22  | CLOCKS                                   |         |

| Table 5-23  | IOM/PCM MUX                              |         |

| Table 5-24  | UART                                     |         |

| Table 5-25  | PEDIU                                    |         |

| Table 5-26  |                                          | 5-19    |

| List of Tab | les                                                        | Page   |

|-------------|------------------------------------------------------------|--------|

| Table 5-27  | OAK MAIL BOX                                               | 5-20   |

| Table 5-28  |                                                            |        |

| Table 5-29  |                                                            | 5-26   |

| Table 5-30  |                                                            |        |

| Table 5-31  |                                                            |        |

| Table 5-32  |                                                            |        |

| Table 5-33  |                                                            |        |

| Table 5-34  |                                                            |        |

| Table 5-35  |                                                            |        |

| Table 5-36  |                                                            | 5-37   |

| Table 5-37  |                                                            | 5-38   |

| Table 5-38  |                                                            |        |

| Table 5-39  | Downstream                                                 |        |

| Table 5-40  | Upstream                                                   |        |

| Table 5-41  | Time-Slot Encoding for Data Memory Accesses                |        |

| Table 5-42  | Time-Slot Encoding for Control Memory Accesses             |        |

| Table 5-43  |                                                            | 5-46   |

| Table 5-44  | Summary of MF-Channel Commands                             |        |

| Table 5-45  |                                                            |        |

| Table 5-46  |                                                            |        |

| Table 5-47  |                                                            |        |

| Table 6-1   | An Example for Required DSP Performance in a Comfort PBX   |        |

|             | with 30 Subscribers                                        | . 6-10 |

| Table 7-1   |                                                            |        |

| Table 7-2   |                                                            |        |

| Table 7-3   |                                                            |        |

| Table 7-4   |                                                            |        |

| Table 7-5   |                                                            |        |

| Table 7-6   | Bus Interface Timing                                       |        |

| Table 7-7   | Siemens/Intel Interrupt Timing                             |        |

| Table 7-8   | Motorola Interrupt Timing                                  |        |

| Table 7-9   | Interrupt Timing                                           |        |

| Table 7-10  | PDC and PFS Timing In Master Mode                          |        |

| Table 7-11  | PCM-Interface Timing in Master Mode                        |        |

| Table 7-12  | PCM Interface Timing In Slave Mode                         |        |

| Table 7-13  | IOM®-2 Interface Clocks Timing when FSC and DCL are Driven |        |

|             | by ELICO and the DOC is in Slave Mode                      | . 7-20 |

| Table 7-14  | IOM®-2 Interface Clocks Timing When FSC and DCL are Driven | •      |

| . 30.0 1 11 | directly by PDC4/8 and PFS, and the DOC is in Slave Mode   | . 7-22 |

| Table 7-15  | IOM®-2 Interface Clocks Timing when FSC and DCL are Driven |        |

|             | Directly by PDC4/8 and PFS, and the DOC is in Master Mode  |        |

|             | (PDC and PES are generated by internal clocks generator)   | 7-23   |

| List of Tabl | les                                  | Page   |

|--------------|--------------------------------------|--------|

| Table 7-16   | IOM®-2 Interface Timing              | . 7-24 |

| Table 7-17   | FSCD (Delayed FSC) Timing            |        |

| Table 7-18   | Channel Indication (CHI) Timing      | . 7-27 |

| Table 7-19   | DRDY Timing                          |        |

| Table 7-20   | Serial Interface Timing              | . 7-28 |

| Table 7-21   | Reset Timing                         | . 7-33 |

| Table 7-22   | Boundary Scan Timing                 | . 7-34 |

| Table 7-23   | Program Read Access Timing           | . 7-35 |

| Table 7-24   | External Data Read Access Timing     | . 7-37 |

| Table 7-25   | External Program/Data Write Access   | . 7-41 |

| Table 7-26   | CLK61 (input) Timing                 | . 7-45 |

| Table 7-27   | CLK16 (input) Timing                 |        |

| Table 7-28   | REFCLK Timing                        | . 7-46 |

| Table 7-29   | XCLK (input) Timing                  | . 7-47 |

| Table 7-30   | CLK30 (output) Timing                | . 7-48 |

| Table 7-31   | CLK15 (output) Timing                | . 7-48 |

| Table 7-32   | CLK7 (output) Timing                 | . 7-49 |

| Table 9-1    | Timing Characteristics of the IOM®-2 |        |

| Table 9-2    | Timing Characteristics of the IOM®-2 | 9-4    |

Overview

#### 1 Overview

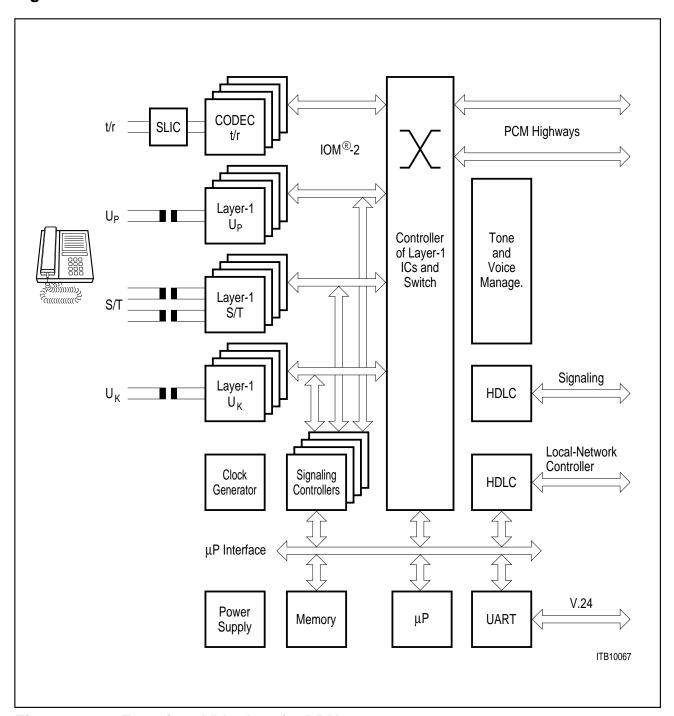

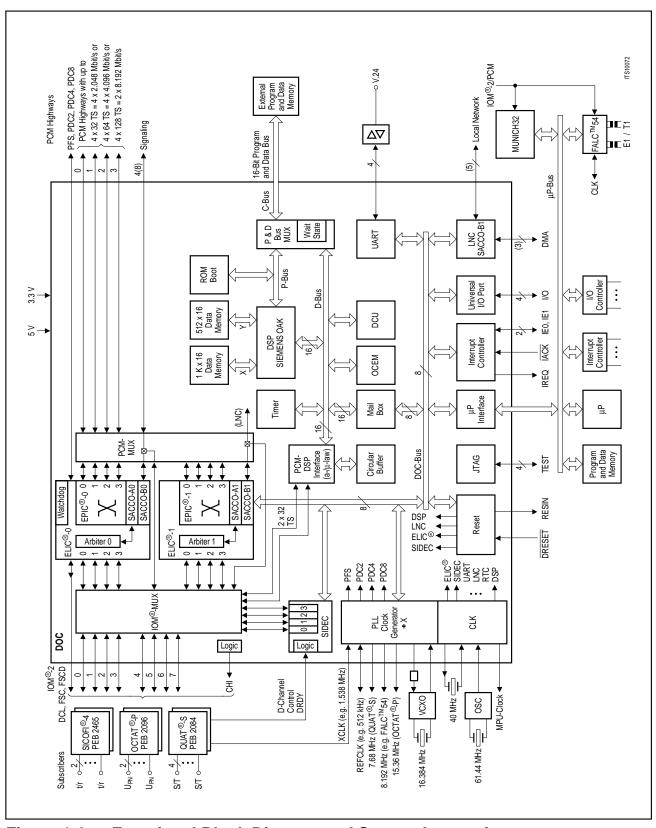

A Small PBX and a Line Card consist of the following main functional blocks: A switching matrix, multiple Layer-1 transceivers for t/r (a/b), S/T,  $U_P$  and  $U_K$  interfaces, IOM-2 interface controller, signaling controllers, a DSP for tone and voice management, a microprocessor, memory, clock generator, power supply and transformers.

Figure 1-1 shows main functional blocks of a PBX.

Figure 1-1 Functional Blocks of a PBX

The new Siemens generation of highly integrated ISDN circuits enables design engineers to decrease board size and thus PBX size and its production costs.

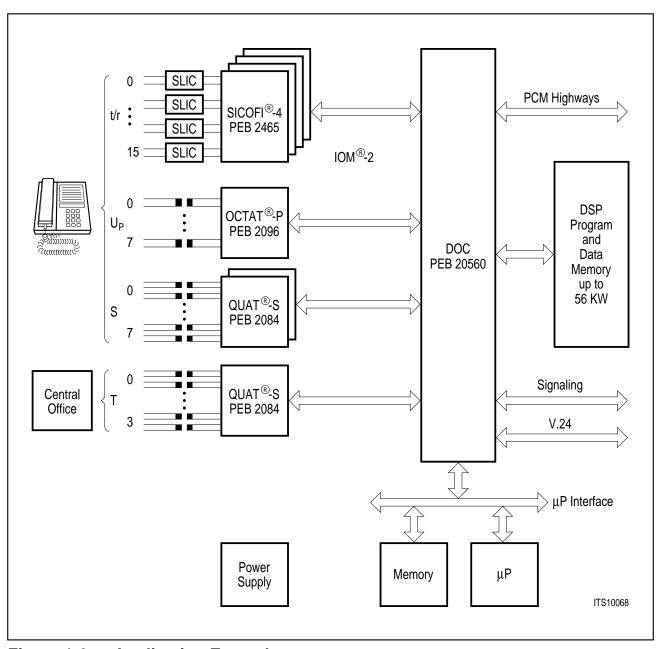

**Figure 1-2** shows an example of a PBX for 16 ISDN and 16 analog subscribers with 4 trunk lines realized with a few highly integrated chips of the new Siemens family of PBX and Line Card ICs: DOC, SICOFI-4, OCTAT-P and QUAT-S.

Figure 1-2 Application Example

PBX for 32 Subscribers with 4 Trunk Lines using one DOC

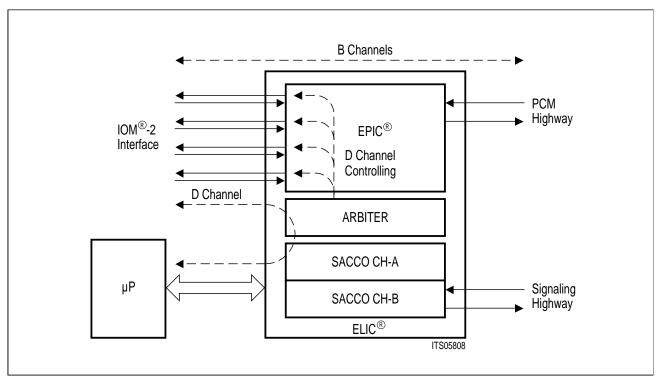

**DOC**, DSP Oriented PBX Controller, PEB 20560, The DOC integrates many different functional blocks on a single chip for building small PBXs or PBX Line Cards: Two ELICs, Enhanced Line Card Controller (PEB 20550), one SIDEC, 4-channel signaling controller

(LAP-D), multiple IOM-2 and PCM interfaces, one up-to 40 MIPS DSP with on-chip emulation and a Mailbox, one PCM-DSP interface for fast DSP access, one UART, Interrupt Controller, ...

The DOC is a CMOS device offered in a P-MQFP-160 package.

**QUAT**<sup>®</sup>-**S**, Quadruple Transceiver for S/T Interfaces, PEB 2084, implements 4 four-wire S/T interfaces to link voice/data digital terminals to PBX subscriber lines and PBX trunk lines to the public ISDN. It can handle up to four S/T interfaces simultaneously in accordance with CCITT I.430, ETSI 300.012, and ANSI T1.605 standards.

The QUAT-S is a CMOS device offered in a P-MQFP-44 package.

**OCTAT**<sup>®</sup>-**P**, Octal Transceiver for  $U_{PN}$  interfaces, PEB 2096, implements the two-wire  $U_{PN}$  interface used to link voice/data digital terminals to PBX subscriber lines. The OCTAT-P is an optimized device for LT applications and can handle up to eight  $U_{PN}$  interfaces simultaneously. It handles the  $U_{PN}$  interfaces in accordance with the  $U_{P0}$  interface specification except for the reduced loop length.

The OCTAT-P is a CMOS device offered in a P-MQFP-44 package.

**SICOFI®-4,** Programmable signaling and CODEC Filter with 4 channels, PEB 2465, implements 4 t/r (a/b) interfaces to link analog voice terminals to PBX subscriber lines and analog PBX trunk lines to public switches. An integrated Digital Signal Processor handles all the algorithms necessary e.g. transhybrid-loss adaption, gain, frequency response, impedance matching. The IOM-2 Interface handles digital voice transmission, SICOFI-4 feature control and transparent access to the SICOFI-4 command and indication pins. To program the filters, precalculated sets of coefficients are downloaded from the system to the on-chip coefficient RAM. Thus it is possible to use the same line card in different countries.

The SICOFI-4 is a CMOS device offered in P-MQFP-64 package.

### ISDN-Oriented Modular Interface (IOM®-2)

The "Group of Four", ALCATEL, Siemens, Plessey and ITALTEL systems houses, originally defined a General Circuit Interface (GCI) with the aim of specifying a comprehensive interface which would allow various telecommunication devices to communicate in an efficient manner. The IOM-2 interface is a four-wire interface. It became a standard interface for interchip communication in ISDN applications. All above ICs are compatible and operate from a single 5 V power supply (incl. SICOFI-4).

#### **DSP Oriented PBX Controller (DOC)**

The DOC is comprising all necessary functional blocks like switching, signaling, DTMF/tone handling and conferencing on a single chip.

The transceivers (layer 1 ICs) are not integrated.

Figure 1-3 Principle Block Diagram of the DOC

# **DSP Oriented PBX Controller DOC**

**PEB 20560**

Version 2.1 CMOS

#### 1.1 DOC Features

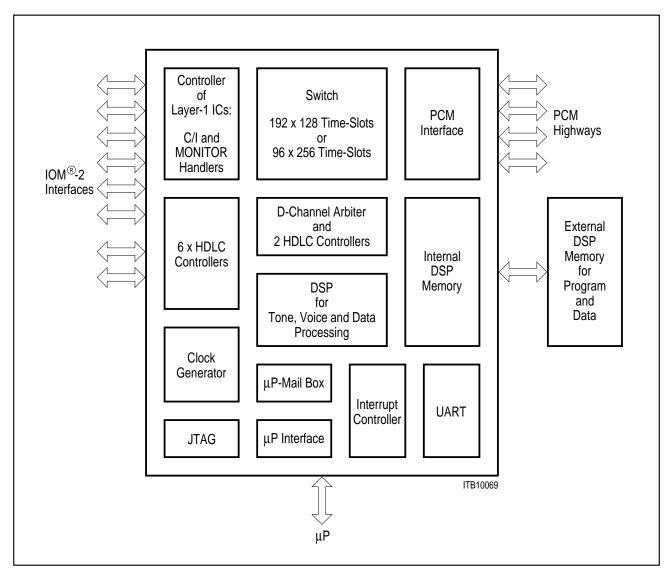

The DOC provides all necessary features for building PBX (Privat Branch eXchange) systems and Line Cards.

- In the PBX mode (Figure 2-1), the DOC provides:

- 6 fully usable IOM-2 (GCI) interfaces and thus it can control up to 48 ISDN or 96 analog subscribers.

- 4 PCM highways with 128 time-slots in total.

- In the Line Card mode (**Figure 2-3**), the DOC provides:

- 2 fully usable IOM-2 interfaces with 16 IOM-2 subframes (2  $\times$  8) and

- 2 limited IOM-2 interfaces, as two DSP ports are connected,

and thus it can control 16 to 24 ISDN (or 32 to 48 analogue) subscribers.

- 4 PCM highways with 256 time-slots in total.

- Signaling via 8 assignable HDLC controllers, each with a 64-byte data FIFO for transmit and for receive direction.

- 2 HDLC controllers (SACCO-A) assignable to two of up to 48 ISDN subscribers at a time via two different D-channel Arbiters

- 4 HDLC controllers (SIDEC) assignable to any D-/B-channel in data upstream or data downstream direction on four IOM-2 interfaces.

- 2 HDLC controllers (SACCO-B) assignable to any time-slot in data upstream or data downstream direction of the four IOM-2 interfaces or the PCM highways.

Optionally, both controllers can be used as stand alone HDLC controllers with up to 8.192 Mbit/s transfer rate. They support DMA operation.

- On-chip user programmable 16-bit Digital Signal Processor, Siemens OAK, (with 20, 30 or up to 40 MIPS) with access to 64 time-slots (via one or two internal IOM-2 interfaces) for DTMF/Tone generation and recognition, conferencing, music-on-hold, modem emulation, etc.

- $-1 \text{ K} \times 16$ -bit on-chip data memory (X)

- 512 × 16-bit on-chip data memory (Y)

| Туре           | Ordering Code | Package      |

|----------------|---------------|--------------|

| PEB 20560 V2.1 | Q67231-H1007  | P-MQFP-160-1 |

DSP proprietary interface to an external memory:

\* Program memory up to 56 K  $\times$  16-bit \* Data memory up to 32 K  $\times$  16-bit - On-chip program ROM (Boot)  $\sim$  0.5 K  $\times$  16-bit

- a-/μ-law coding and decoding by hardware (on the fly)

- Firmware for DSP work load measurement (within every 125 μs frame)

- Protection against write into program memory using password

- μP-DSP communication via two Mail-Boxes

- On-chip emulation (OCEM) for DSP program debugging

- 8-bit μP Interface compatible with Siemens/Intel bus schemes

- Programmable clock generator with built-in logic for Master and Slave configurations

- Watch-Dog timer

- Reset logic

- UART for V.24 Interface

- Multifunctional Input/Output Port configurable as a general I/O Port, DMA lines for SACCO-B0 or as additional UART lines for Modem connection

- · Integrated Interrupt controller with vector generation and support for DOC cascading

- Interrupt vector handling compatible with Siemens/Intel/Motorola bus schemes

- Up to 4 external interrupt inputs (via the general I/O Port)

- · JTAG Interface for on board tests

- Interface for HW and SW DSP evaluation (debugging)

- Advanced CMOS 0.5 μm technology

- 3.3-V and 5-V Power Supply in 5-V environment

3.3-V Power Supply in 3.3-V environment

- TTL driving capability, TTL and CMOS compatible inputs

- P-MQFP-160 package

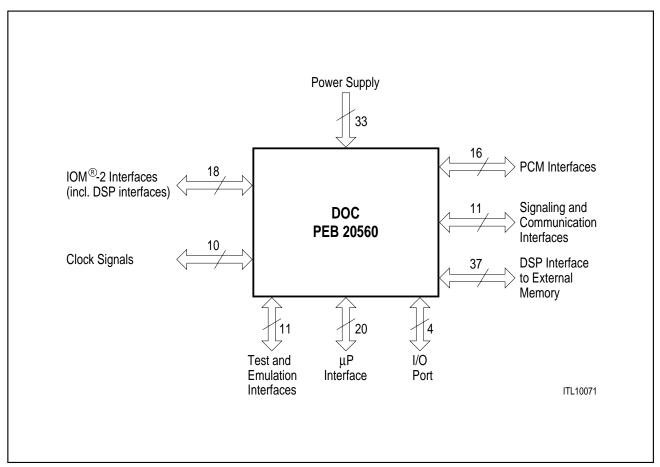

#### 1.2 Logic Symbol

Figure 1-4 DOC Logic Symbol

(160 pins are used)

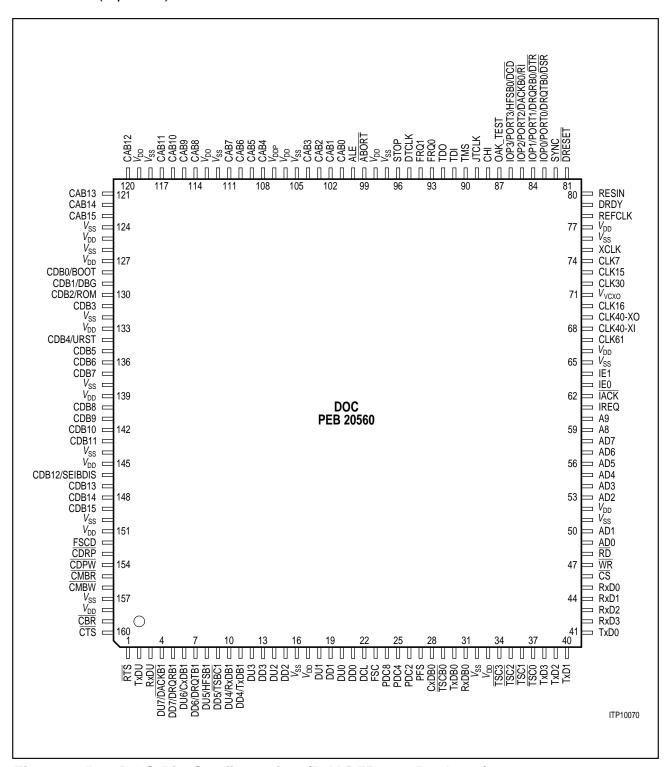

### 1.3 Pin Configuration

(top view)

Figure 1-5 DOC Pin Configuration (P-MQFP-160 Package)

### 1.4 Pin Description

Table 1-1 IOM®-2 Interface

| Pin<br>No. | Symbol        | In (I)<br>Out (O) | During<br>Reset                      | Function                                                                                                                                                                                                                                                                                                                                              |

|------------|---------------|-------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | FSC           | I/O               | I                                    | Frame Synchronization Clock (8 kHz)                                                                                                                                                                                                                                                                                                                   |

| 22         | DCL           | I/O               | I                                    | Data CLock: Single or double data rate.                                                                                                                                                                                                                                                                                                               |